Знакомство с принципом работы мультиплексора и демультиплексора; получение навыков работы по определению временных диаграмм и составлению таблиц соответствия

ЛАБОРАТОРНАЯ РАБОТА №1

МУЛЬТИПЛЕКСОРЫ И

ДЕМУЛЬТИПЛЕКСОРЫ

Цель работы: знакомство с принципом

работы мультиплексора и демультиплексора; получение навыков работы по определению временных диаграмм и составлению таблиц

соответствия.

ОСНОВНЫЕ ПОНЯТИЯ

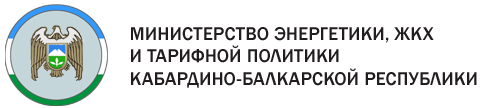

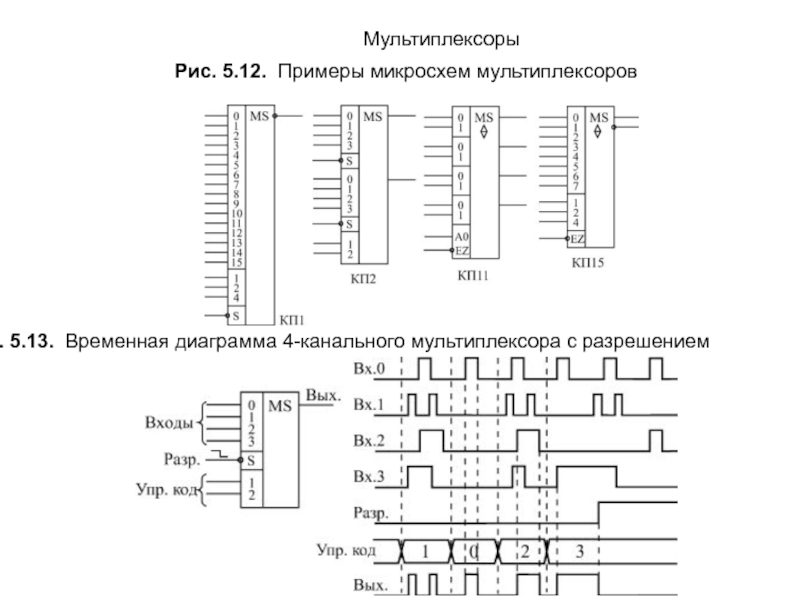

Мультиплексоры

и демультиплексоры – логические схемы, осуществляющие многопозиционную

коммутацию цифровых сигналов.

Мультиплексор

– логическая схема, осуществляющая коммутацию цифровых сигналов с одного входа

на один из нескольких выходов, в зависимости от состояния адресных входов (кода

адреса).

Демультиплексор

– логическая схема, осуществляющая коммутацию цифровых сигналов с одного из

нескольких входов на один выход, в зависимости от состояния адресных входов

(кода адреса).

Входы:

информационные; адресные и разрешающие (стробирующие) (служебные).

Выходы:

информационные (прямые и/или инверсные).

Мультиплексоры

могут быть объединены для наращивания разрядности. 2 способа: в пирамидальную

схему либо последовательным соединением разрешающих входов и внешних логических

элементов. Так же могут быть объединены демультиплексоры.

ИСХОДНЫЕ ДАННЫЕ

Мультиплексор:

1) 0110

2) 10010011

Демультиплексор:

1) 1000

2) 10010001

РЕЗУЛЬТАТЫ ПРОВЕДЕНИЯ РАБОТЫ

Таблицы

соответствия:

Таблица 1 –

четырехразрядный мультиплексор:

Двоичный код числа на входе мультиплексора | № тактового импульса | Адресный вход Х1 | Адресный вход Х2 | Выход У | |||

D0 | D1 | D2 | D3 | ||||

0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 |

0 | 1 | 1 | 0 | 2 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 3 | 1 | 0 | 1 |

0 | 1 | 1 | 0 | 4 | 1 | 1 | 0 |

Таблица 2 –

восьмиразрядный мультиплексор:

Двоичный код числа на входе мультиплексора | № тактового импульса | Адресный вход Х1 | Адресный вход Х2 | Адресный вход Х3 | Выход У | |||||||

D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | |||||

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 2 | 0 | 0 | 1 | 0 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 3 | 0 | 1 | 0 | 0 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 4 | 0 | 1 | 1 | 1 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 5 | 1 | 0 | 0 | 0 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 6 | 1 | 0 | 1 | 0 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 7 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 8 | 1 | 1 | 1 | 1 |

Таблица 3 –

четырехразрядный демультиплексор:

Двоичный код числа на входе мультиплексора | № тактового импульса | Адресный вход Х1 | Адресный вход Х2 | Выходы | |||

У0 | У1 | У2 | У3 | ||||

1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

0 | 2 | 0 | 1 | 1 | 1 | 1 | 1 |

0 | 3 | 1 | 0 | 1 | 1 | 1 | 1 |

0 | 4 | 1 | 1 | 1 | 1 | 1 | 1 |

Таблица 4 –

восьмиразрядный демультиплексор:

Двоичный код числа на входе | № тактового импульса | Адресный вход Х1 | Адресный вход Х2 | Адресный вход Х3 | Выходы |

У0 У1 У2 У3 У4 У5 У6 У7 | |||||

1 | 1 | 0 | 0 | 0 | 0 1 1 1 1 1 1 |

0 | 2 | 0 | 0 | 1 | 1 1 1 1 1 1 1 |

0 | 3 | 0 | 1 | 0 | 1 1 1 1 1 1 1 |

1 | 4 | 0 | 1 | 1 | 1 1 1 0 1 1 1 |

0 | 5 | 1 | 0 | 0 | 1 1 1 1 1 1 1 |

0 | 6 | 1 | 0 | 1 | 1 1 1 1 1 1 1 |

0 | 7 | 1 | 1 | 0 | 1 1 1 1 1 1 1 |

1 | 8 | 1 | 1 | 1 | 1 1 1 1 1 1 1 |

Временные диаграммы:

Диаграмма 1 – четырехразрядный мультиплексор:

Диаграмма 2 – восьмиразрядный мультиплексор:

Диаграмма 3 – четырехразрядный демультиплексор:

Диаграмма 4 – восьмиразрядный демультиплексор:

Вывод. В

В

процессе выполнения работы мы на практике познакомились с работой

мультиплексора и демультиплексора, а также получили практические навыки по

составлению временных диаграмм и таблиц соответствия.

Цифровые схемы — мультиплексоры — CoderLessons.com

Мультиплексор — это комбинационная схема, которая имеет максимум 2 n входов данных, n линий выбора и одну выходную линию. Один из этих входов данных будет подключен к выходу на основе значений линий выбора.

Так как есть n строк выбора, будет 2 n возможных комбинаций нулей и единиц. Итак, каждая комбинация выберет только один ввод данных. Мультиплексор также называется Mux .

4×1 Мультиплексор

Мультиплексор 4×1 имеет четыре входа данных I 3 , I 2 , I 1 и I 0 , две строки выбора s 1 & s 0 и один выход Y. Блок-схема мультиплексора 4×1 показана на следующем рисунке.

Один из этих 4 входов будет подключен к выходу на основе комбинации входов, присутствующих в этих двух линиях выбора. Таблица истинности мультиплексора 4×1 показана ниже.

Таблица истинности мультиплексора 4×1 показана ниже.

| Линии выбора | Выход | |

|---|---|---|

| S 1 | S 0 | Y |

| 0 | 0 | Я 0 |

| 0 | 1 | Я 1 |

| 1 | 0 | Я 2 |

| 1 | 1 | Я 3 |

Из таблицы Truth мы можем напрямую написать булеву функцию для вывода, Y как

Y=S1′S0′I0+S1′S0I1+S1S0′I2+S1S0I3

Мы можем реализовать эту булеву функцию с помощью инверторов, вентилей AND и вентиля OR. Принципиальная схема мультиплексора 4×1 показана на следующем рисунке.

Мы можем легко понять работу вышеупомянутой схемы. Аналогично, вы можете реализовать мультиплексор 8×1 и мультиплексор 16×1, следуя той же процедуре.

Реализация мультиплексоров высшего порядка.

Теперь давайте реализуем следующие два мультиплексора высшего порядка, используя мультиплексоры низкого порядка.

- 8×1 мультиплексор

- 16×1 мультиплексор

8×1 мультиплексор

В этом разделе мы реализуем мультиплексор 8×1, используя мультиплексоры 4×1 и мультиплексор 2×1. Мы знаем, что 4×1 Multiplexer имеет 4 входа данных, 2 строки выбора и один выход. Принимая во внимание, что мультиплексор 8×1 имеет 8 входов данных, 3 строки выбора и один выход.

Итак, нам требуется два мультиплексора 4×1 на первом этапе, чтобы получить 8 входных данных. Поскольку каждый мультиплексор 4×1 производит один выходной сигнал, нам требуется мультиплексор 2×1 на втором этапе, рассматривая выходы первого этапа в качестве входных данных и для получения конечного выхода.

Пусть мультиплексор 8×1 имеет восемь входов данных от I 7 до I 0 , три строки выбора s 2 , s 1 & s0 и один выход Y. Таблица истинности мультиплексора 8×1 показана ниже.

Таблица истинности мультиплексора 8×1 показана ниже.

| Выбор входов | Выход | ||

|---|---|---|---|

| S 2 | S 1 | S 0 | Y |

| 0 | 0 | 0 | Я 0 |

| 0 | 0 | 1 | Я 1 |

| 0 | 1 | 0 | Я 2 |

| 0 | 1 | 1 | Я 3 |

| 1 | 0 | 0 | Я 4 |

| 1 | 0 | 1 | Я 5 |

| 1 | 1 | 0 | Я 6 |

| 1 | 1 | 1 | Я 7 |

Мы можем легко реализовать мультиплексор 8×1, используя мультиплексоры низкого порядка, рассмотрев приведенную выше таблицу истинности. Блок-схема мультиплексора 8×1 показана на следующем рисунке.

Блок-схема мультиплексора 8×1 показана на следующем рисунке.

Те же строки выбора, s 1 и s 0 , применяются к обоим мультиплексорам 4×1. Входы данных верхнего мультиплексора 4×1 — от I 7 до I 4, а входы данных нижнего мультиплексора 4×1 — от I 3 до I 0 . Таким образом, каждый мультиплексор 4×1 создает выходной сигнал на основе значений строк выбора, s 1 и s 0 .

Выходы мультиплексоров 4×1 первой ступени применяются в качестве входов мультиплексора 2×1, который присутствует на второй ступени. Другая строка выбора s 2 применяется к мультиплексору 2×1.

Если s 2 равно нулю, то выход мультиплексора 2×1 будет одним из 4 входов от I 3 до I 0 на основе значений линий выбора s 1 & s 0 .

Если s 2 равно единице, то выход мультиплексора 2×1 будет одним из 4 входов от I 7 до I 4 на основе значений линий выбора s 1 & s 0 .

Если s 2 равно нулю, то выход мультиплексора 2×1 будет одним из 4 входов от I 3 до I 0 на основе значений линий выбора s 1 & s 0 .

Если s 2 равно единице, то выход мультиплексора 2×1 будет одним из 4 входов от I 7 до I 4 на основе значений линий выбора s 1 & s 0 .

Таким образом, общая комбинация двух мультиплексоров 4×1 и одного мультиплексора 2×1 работает как один мультиплексор 8×1.

16×1 мультиплексор

В этом разделе мы реализуем мультиплексор 16×1, используя мультиплексоры 8×1 и мультиплексор 2×1. Мы знаем, что мультиплексор 8×1 имеет 8 входов данных, 3 строки выбора и один выход. Принимая во внимание, что мультиплексор 16×1 имеет 16 входов данных, 4 строки выбора и один выход.

Итак, нам требуется два мультиплексора 8×1 на первом этапе, чтобы получить 16 входных данных. Так как каждый мультиплексор 8×1 производит один выход, нам требуется мультиплексор 2×1 на втором этапе, рассматривая выходы первого этапа в качестве входных данных и для получения конечного выхода.

Пусть мультиплексор 16×1 имеет шестнадцать входов данных от I 15 до I 0 , четыре строки выбора от s 3 до s 0 и один выход Y. Таблица истинности мультиплексора 16×1 показана ниже.

| Выбор входов | Выход | |||

|---|---|---|---|---|

| S 3 | S 2 | S 1 | S 0 | Y |

| 0 | 0 | 0 | 0 | Я 0 |

| 0 | 0 | 0 | 1 | Я 1 |

| 0 | 0 | 1 | 0 | Я 2 |

| 0 | 0 | 1 | 1 | Я 3 |

| 0 | 1 | 0 | 0 | Я 4 |

| 0 | 1 | 0 | 1 | Я 5 |

| 0 | 1 | 1 | 0 | Я 6 |

| 0 | 1 | 1 | 1 | Я 7 |

| 1 | 0 | 0 | 0 | Мне 8 |

| 1 | 0 | 0 | 1 | Мне 9 |

| 1 | 0 | 1 | 0 | Мне 10 |

| 1 | 0 | 1 | 1 | Мне 11 |

| 1 | 1 | 0 | 0 | Мне 12 |

| 1 | 1 | 0 | 1 | Мне 13 |

| 1 | 1 | 1 | 0 | Мне 14 |

| 1 | 1 | 1 | 1 | Мне 15 |

Мы можем легко реализовать мультиплексор 16×1, используя мультиплексоры низкого порядка, рассмотрев приведенную выше таблицу истинности. Блок-схема мультиплексора 16×1 показана на следующем рисунке.

Блок-схема мультиплексора 16×1 показана на следующем рисунке.

Те же строки выбора, s 2 , s 1 и s 0 , применяются к обоим мультиплексорам 8×1. Входы данных верхнего мультиплексора 8×1 — от I 15 до I 8, а входы данных нижнего мультиплексора 8×1 — от I 7 до I 0 . Следовательно, каждый мультиплексор 8×1 создает выходной сигнал на основе значений строк выбора, s 2 , s 1 & s 0 .

Выходы мультиплексоров 8×1 первой ступени применяются в качестве входов мультиплексора 2×1, который присутствует на второй ступени. Другая строка выбора s 3 применяется к мультиплексору 2×1.

Если s 3 равно нулю, то выход мультиплексора 2×1 будет одним из 8 входов от 7 до I 0 на основе значений линий выбора s 2 , s 1 & s 0 .

Если s 3 равен единице, то выход мультиплексора 2×1 будет одним из 8 входов от I 15 до I 8 на основании значений линий выбора s 2 , s 1 & s 0 .

Если s 3 равно нулю, то выход мультиплексора 2×1 будет одним из 8 входов от 7 до I 0 на основе значений линий выбора s 2 , s 1 & s 0 .

Если s 3 равен единице, то выход мультиплексора 2×1 будет одним из 8 входов от I 15 до I 8 на основании значений линий выбора s 2 , s 1 & s 0 .

Таким образом, общая комбинация двух мультиплексоров 8×1 и одного мультиплексора 2×1 работает как один мультиплексор 16×1.

Мультиплексоры и селекторы — Мегаобучалка

Мультиплексоры. Этофункциональный узел ЭВМ, осуществляющий микрооперацию передачи сигнала с одного из своих входов на один выход. На рисунке 2.25 показаны схема и функциональное обозначение стробируемого мультиплексора К155КП7.

Рисунок 2.25 – Мультиплексор К155КП7

Структура этого узла описывается следующими уравнениями:

Вход V используется для стробирования и наращивания числа входов мультиплексора. Входы a4, a2 и а1 – адресные. Двоичный код на этих входах определяет, какой сигнал Di, будет передан на выход. Например, при a4 = 1, a2 = 0, а1 = 1, V = 0 сигнал D5 передается на выход, так как все остальные члены в формуле при этом наборе будут равны нулю, т. е. y1 =D5, a y2 = . Способ наращивания мультиплексоров (до 16 входов) показан на рисунке 2.26.

Рисунок 2.26 – Наращивание мультиплексоров

Селекторы.Селектор (демультиплексор) – функциональный узел, осуществляющий операцию передачи сигнала с одного входа на один из нескольких выходов. Селекторы в виде самостоятельных узлов изготовляются редко, так как их функции может выполнять дешифратор. Очевидно, что входной сигнал активизирует тот выход дешифратора, который соответствует конкретному набору переменных, являющихся в данном случае адресом селектора. Использование дешифратора для мультиплексирования показано на рисунке 2.27.

Рисунок 2.27 – Селектор-мультиплексор 564КП2

Широкие возможности предоставляет мультиплексор-селектор, выполненный на КМДП-структурах. На рисунке 2.27 показаны схема и функциональное обозначение микросхемы 564КП2. Один из восьми выходов дешифратора, задаваемый адресом а4а2а1 при V = 0, открывает соответствующий двунаправленный ключ Кл, обеспечивая связь цепей у и Di. При V = 1 все ключи закрыты. Данная схема может использоваться в качестве дешифратора с активным уровнем выходов «1» или «0» и мультиплексора. При использовании схемы в качестве дешифратора с уровнем выходов «1» необходимо присоединить цепь у к источнику питания, а цепи Di через резисторы не менее 20 кОм – к земле.

При использовании схемы в качестве дешифратора с активным уровнем выходов «0» необходимо присоединить цепь у к земле, а цепи Diчерез резисторы не менее 20 кОм – к источнику питания. Входами дешифратора будут входы а4, а2, а1, а выходами – Di. При использовании схемы в качестве мультиплексора адресными входами являются входы а4, а2, а1; информационными входами – Di, а выходом – у.

При использовании схемы в качестве селектора адресными входами являются входы а4, а2, а1, информационным входом – у, а выходами Di. Из приведенных примеров следует, что мультиплексоры и селекторы являются многофункциональными узлами.

Счётчики импульсов

Подсчет числа импульсов является наиболее распространенной операцией в устройствах цифровой обработки информации. В устройствах цифровой обработки информации измеряемый параметр (угол поворота, перемещение, скорость, частота, время, температура и т. д.) преобразуется в импульсы напряжения, число которых в соответствующем масштабе характеризует значение данного параметра. Эти импульсы подсчитываются счетчиками импульсов и выражаются в виде цифр.

По целевому назначению счетчики подразделяют на простые и реверсивные. Простые счетчики, в свою очередь, подразделяют на суммирующие и вычитающие. Суммирующий счетчик предназначен для выполнения счета в прямом направлении, т. е. для сложения. С приходом очередного счетного импульса на вход счетчика его показание увеличивается на единицу. Вычитающий счетчик служит для осуществления счета в обратном направлении, т. е. для вычитания. Каждый счетный импульс, поступающий на вход вычитающего счетчика, уменьшает его показание на единицу.

Реверсивные счетчики предназначены для выполнения операции счета как в прямом, так и в обратном направлении, т. е. они могут работать в режиме сложения и вычитания. Основными параметрами счетчиков являются модуль счета (коэффициент счета К) и быстродействие.Коэффициент счета определяет число импульсов, которое может быть сосчитано счетчиком.

Быстродействие счетчика характеризуется максимальной частотой fсч следования счетных импульсов и связанным с ней временем tуст установки счетчика. Величина tуст определяет максимальное время протекания переходных процессов во всех разрядах счетчика с поступлением на вход очередного счетного импульса.Счетчики импульсов выполняются на основе триггеров. Счет числа поступающих импульсов производится с использованием двоичной системы счисления.

Двоичные суммирующие счетчики с непосредственной связью: они производят счет поступающих импульсов в двоичной системе счисления. Основным узлом двоичного счетчика (служащим также его разрядом) является триггер со счетным запуском, осуществляющий подсчет импульсов по модулю 2.

Многоразрядные двоичные суммирующие счетчики с непосредственной связью выполняются путем последовательного соединения счетных триггеров. Принцип действия двоичного счетчика с непосредственной связью рассмотрим на примере четырехразрядного счетчика, показанного на рисунке 2.28. Схема выполнена на счетных Тt-триггерах с внутренней задержкой. Работу схемы иллюстрируют временные диаграммы, приведенные на рисунке 2.28, и таблица 2.4.

Рисунок 2.28 – Двоичный четырёхразрядный счётчик

По окончании 15-го импульса все разряды счетчика устанавливаются в состояние «1», а 16-й импульс переключает первый разряд счетчика в «0». В соответствии с рисунком 2.28 и таблицей 2.4, установка в исходное состояние «0» двух последовательно включенных триггеров (DD1 и DD2) осуществляется четвертым счетным импульсом, трех триггеров (DD1-DD3) – восьмым и четырех триггеров – 16-м счетным импульсом. Из этого следует, что модуль счета двухразрядного, трехразрядного и четырехразрядного двоичных счетчиков равен соответственно 4, 8 и 16. Модуль счета двоичного счетчика находят из соотношения Ксч = 2N,где N – число разрядов счетчика.

В процессе работы двоичного счетчика частота следования импульсов на выходе каждого последующего триггера уменьшается вдвое по сравнению с частотой его входных импульсов. Это свойство схемы используют для построения делителей частоты.При использовании схемы в качестве делителя частоты входной сигнал подают на счетный вход первого триггера, а выходной снимают с последнего триггера.

Выходная и входная частоты связаны соотношением fвых = fвх/Ксч.Максимальное время установки tуст max в двоичных счетчиках с непосредственной связью характеризуется суммарной задержкой в последовательной передаче информации от младшего к старшему разрядусчетчика. Другими словами, параметр определяется временем перехода счетчика из кода 2N – 1 в код 00…0. Его находят из соотношения tуст max = Ntзт , где tзт – задержка переключения Тt-триггера после окончания счетного импульса.

Таблица 2.4 – Состояние триггеров счётчика

| Число импульсов | Триггер 1 | Триггер 2 | Триггер 3 | Триггер 4 |

| 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 1 | |

| 0 | 0 | 1 | 0 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 0 | |

| 0 | 1 | 1 | 1 | |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 0 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 1 | |

| 0 | 0 | 0 | 0 |

Время установки возрастает с увеличением числа разрядов, что сказывается на быстродействии счетчика. Максимальная частота следования счетных импульсов ограничивается величиной:

fвх max = 1/(tи + tуст max) . (2.13)

При работе счетчика в режиме деления частоты его предельная частота определяется предельной частотой переключения триггера первого разряда:

fвх max = 1/(tи + tзт) . (2.14)

Счетчики с коэффициентом счета Ксч ¹ 2N.

На практике часто возникает необходимость в счетчиках, коэффициент счета которых не соответствует указанному значению 2N. Такие счетчики выполняются на основе двоичных счетчиков. Общий принцип их построения основывается на исключении у счетчика с Ксч = 2N соответствующего числа «избыточных» состояний. Число избыточных состояний s определяется разностью: s = 2N – Ксч, где 2N – количество состояний двоичного счетчика; Ксч – требуемый коэффициент счета. Число триггеров счётчика выбирают по минимуму величины s. Например, при построении счетчика с Ксч = 3на двух триггерах и счетчика с Ксч = 10 на четырех триггерах следует исключить соответственно 1 и 6 состояний.

Способы построения счетчиков с коэффициентом счета Ксч ¹ 2N достаточно разнообразны. Наибольшее распространение получили способ принудительной установки в состояние «0» всех разрядов двоичного счетчика и способ принудительного насчета. По первому способу реализуются счетчики с естественным порядком счета, по второму – счетчики с принудительным счетом.

В счетчиках с естественным порядком счета порядок счета такой же, как в двоичных счетчиках. Отличие заключается в том, что путем введения дополнительных связей счет заканчивается раньше значения 2N. У счетчика с Ксч = 10 переход разрядов в состояние «0» будет происходить с приходом не 16-го, а 10-го счетного импульса («Система 16 – 6»).

В счетчиках с принудительным насчетом исключение избыточных состояний двоичного счетчика достигается путем принудительной установки отдельных его разрядов всостояние «1» в процессе счета. Принудительный насчет осуществляется введением обратных связей со старших разрядов двоичного счетчика в младшие, благодаря чему соответствующие младшие разряды вне очередипереключаются в состояние «1».

Вследствие принудительного насчета показания рассматриваемых счетчиков не соответствуют двоичной системе счисления. По этой причине их относят к классу счетчиков с «произвольным» порядком счета. Способ реализации счетчиков с принудительным насчетом показан на примере функциональной схемы счетчика с Ксч = 10 (рисунок 2.29).

Рисунок 2.29 – Функциональная схема декадного счетчика

с принудительным насчетом

До записи «1» в четвертый разряд, т. е. до прихода восьмого счетного импульса, счетчик работает как двоичный (таблица 2.5). С приходом восьмого счетного импульса «1» записывается в триггер Т4 с осуществлением обратной связи на запись «1» во вторую и третью ячейки.

Таблица 2.5 – Состояние триггеров счётчика с принудительным счётом

| Число входных импульсов | Т4 | Т3 | Т2 | Т1 |

| 8*®14 | ||||

Таким образом, после восьмого счетного импульса вследствие принудительного насчета в счетчик записывается число 8 + 6 = 14. Девятый счетный импульс устанавливает «1» в триггере Т1,а десятый счетный импульс возвращает счетчик в исходное нулевое состояние.

Счетчики с Ксч = 10называют десятичными, или декадными. Они нашли широкое применение для регистрации числа импульсов с последующим визуальным отображением результата.

Десятичные счетчики часто включают последовательно (рисунок 2.30).

Рисунок 2.30 – Последовательное соединение декадных счётчиков

Если в пределах всех декад счет ведется в двоичной системе счисления, то, например, числу 978 будет отвечать код1001 0111 1000, характеризующий двоично-десятичную систему счисления.

Электронная промышленность выпускает широкую номенклатуру интегральных схем счётчиков. Типичным представителем является счётчик 531ИЕ16 – синхронный, реверсивный, декадный, двоично-десятичныйсчётчик. Эта ИС позволяет строить счётчики с предустановкой, строить комбинированные схемы счётчиков, управлять их коэффициентом счёта и управлять направлением счёта.

Современными счётчиками КМОП ИС являются микросхемы КР1554ИЕ6, ИЕ7, ИЕ10, ИЕ18 и ИЕ23, имеющие примерное время задержки распространения в диапазоне 9-22 нс.Развитие этой технологии – серии 5514 и 5554. Кроме счётчиков в сериях общего назначения имеются счётчики и в сериях сверхбыстродействующих ИС. Микросхемы серии 6500 (буферизированная полевая логика, материал GaAs) работают на максимальной частоте не менее 1000 МГц и имеют время задержки распространения 1-2 нс. Так, 6500ИЕ4 – 4-разрядный двоичный счётчик с предустановкой. Напряжения питания ИС этой серии – 4 В и минус 2,5 В. Выход – с открытым истоком, сопротивление внешней нагрузки – 50 Ом.

Особо стоит сверхбыстродействующая серия 193, используемая с закрытым входом (с разделительным конденсатором) и имеющая высокую чувствительность, но работающая от конечного значения нижней входной частоты. Так, счётчик К193ИЕ9 с коэффициентом счёта 4 работает на нижней частоте 150 МГц при напряжении 0,6 В и на верхней 1,3 ГГц, а при нескольких милливольтах на частоте 1150 МГц. Счётчик Н193ПЦ5 работает в диапазоне частот 1500-3000 МГц. В этой серии имеются микросхемы для построения сверхвысокочастотных делителей частоты с управляемым коэффициентом деления. У этих ИС есть управляющий вход, изменяющий коэффициент счёта дискретно: так, счётчик 193ИЕ8 имеет управляемый коэффициент счёта 20/22, а микросхема ИЕ2 – коэффициент 10/11.

Сумматоры

Сумматораминазываются логические устройства, выполняющие операцию сложения двух чисел.В зависимости от способа обработки чисел различают последовательные и параллельные сумматоры. Последовательные сумматоры строятся на основе одноразрядной суммирующей схемы. В таких устройствах сложение двух чисел производится поразрядно последовательно во времени. Параллельные сумматоры строят, как правило, на основе композиции одноразрядных суммирующих схем, причем обработка чисел в таких устройствах производится одновременно во всех разрядах. Логическое проектирование в этом случае сводится к синтезу одноразрядных сумматоров и организации цепей переносав соответствии с заданными требованиями на быстродействие [5].

Одноразрядные суммирующие схемы различают по числу входов. Рассмотрим синтез одноразрядных суммирующих схем на два входа аi и Bi: эти схемы часто называются полусумматорами или сумматорами по модулю 2. Выходными сигналами такого устройства являются сумма Сiи перенос Пi, который при суммировании по модулю 2 не используется. Работа полусумматора может быть задана таблицей истинности(таблица 2.6), в соответствии с которой функции выходов Сi и Пi могут быть записаны в виде:

; Пi = AiВi. (2.15)

Таблица 2.6 – Таблица истинности полусумматора

| Аi | Bi | Ci | Пi | |

При построении сумматоров на ИС обычно ставится задача оптимального проектирования для удовлетворения требования максимального быстродействияи обеспечения минимального количества однотипных логических элементов. Быстродействие устройств на ИС в основном определяется задержкой логических элементов НЕ. Поэтому для получения максимального быстродействия сумматоров необходимо проектировать схему с минимальным числом последовательно соединенных элементов НЕ. Отсюда предпочтительным при построении комбинационных схем с максимальным быстродействием является функционально избыточный базис И-ИЛИ-НЕ.

Рассмотрим реализацию полусумматора на логических элементах И-ИЛИ-НЕ. Для этого представим выражение для переключательной функции в виде структурного уравнения:

Сi = ; . (2.16)

Схемное решение для этой функции с учетом цепи образования переноса показано на рисунке 2.31.

Поскольку коэффициент разветвления по выходу логического элемента И внутри интегральных схем, как правило, не превышает единицы, то при реализации переключательной функции Пi для однотипности применяется элемент И-ИЛИ-НЕ, в котором в силу использования только одного входа элементов И выполняется функция ИЛИ-НЕ. Тогда функция Пi может быть представлена структурным уравнением:

Пi = . (2.17)

Рисунок 2.31 – Полусумматор на элементах И-ИЛИ-НЕ

Одноразрядные полные суммирующие схемы (сумматоры на три входа) предназначены для образования выходных сигналов суммы Сi и переносаПi по сигналам на входеAi, Bi, Пi-1. Закон функционирования такого полного сумматора определяется таблицей истинности (таблица 2.7).

Таблица 2.7 – Таблица истинности полного сумматора

| Аi | Bi | Пi-1 | Ci | Пi | |

| 0 | |||||

| 0 | |||||

| 0 | |||||

| 1 | |||||

По этой таблице может быть составлено выражение для переключательных функций Сi и Пi в СДНФ:

; (2.18)

. (2.19)

Эти уравнения можно представить в виде структурных формул, удобных для реализации на логических элементах И-ИЛИ-НЕ. Для удовлетворения требования минимальных аппаратурных затрат используют метод минимизации схем. С этой целью преобразуют выражения так, чтобы обеспечить максимально возможное число общих членов. Структурное уравнение суммы представляется в следующем виде:

; (2.20)

Пi = . (2.21)

Схема, реализующая данные функции, представлена на рисунке 2.32. Быстродействие сумматора определяется временем задержки трех элементов НЕ.

Методы построения параллельных сумматоров на основе каскадного соединения одноразрядных полных сумматоров: различают параллельные комбинационные сумматоры с последовательным, одновременным и комбинированным переносом. Выбор типа переноса между разрядами суммирующего устройства определяется требованиями к его быстродействию.

Рисунок 2.32 – Схема полного сумматора в базисе И-ИЛИ-НЕ

Сумматоры с последовательным переносом имеют сравнительно низкое быстродействие, определяемое временем суммирования при сложении двух n-разрядных чисел. На входы каждой одноразрядной схемы сумматора поступают два слагаемых и перенос из предыдущего разряда. Каждый одноразрядный сумматор вырабатывает сумму и перенос в следующий разряд. Сигнал переноса, образованный в младшем разряде, распространяется последовательно по цепям переноса к старшим разрядам.Поэтому время распространения переноса определяется суммарной задержкой этих цепей.

С целью повышения быстродействия применяют сумматоры с одновременным переносом.У них время распространения переноса не зависит от числа разрядов и определяется только временем задержки схемы переноса. В качестве недостатка сумматоров с одновременным переносом следует отметить значительный рост аппаратурных затрат при построении схем межразрядных переносов,что практически ограничивает возможность такого метода реализации сумматоров. Сложность цепей переноса определяет допустимое число разрядов в таких сумматорах.

В сумматорах с комбинированным переносом полные одноразрядные сумматоры объединяются в группы. Внутри группы, как правило, осуществляется одновременный перенос. Между группами перенос может быть как последовательный, так и одновременный. Организация переноса в комбинационных n-разрядных сумматорах с комбинированным переносом позволяет проектировать схемы, отвечающие предъявляемым требованиям к быстродействию и приемлемые в отношении аппаратурных затрат.

Вопросы для самотестирования

1 Чем характеризуются последовательные регистры (регистры сдвига)? Из чего они состоят?

2 Какие логические устройства называются преобразователями кодов? Какие основные операции входят в процедуру их синтеза?

3 Укажите основные способы построения счётчиков импульсов с коэффициентом счёта, не равным 2n.

4 Охарактеризуйте параметр «импульсная помехоустойчивость» логического элемента.

5 Что характерно для таблицы состояний дешифратора двоично-десятичного кода в единичный десятичный код?

Руководство по эксперименту с

LogicBlocks — learn.sparkfun.com

Добавлено в избранное

Любимый

2

7. Мультиплексор 2-к-1

Мультиплексор (или mux ) — это обычная цифровая схема, используемая для смешивания большого количества сигналов в один. Если вы хотите, чтобы несколько источников данных совместно использовали одну общую строку данных, вы должны использовать мультиплексор, чтобы передать их в эту строку. Мультиплексоры бывают самых разных форм и размеров, но все они состоят из логических вентилей.

Каждый мультиплексор имеет по крайней мере одну строку выбора, которая используется для выбора того, какой входной сигнал будет ретранслироваться на выход. В мультиплексоре 2 к 1 есть только одна строка выбора. Больше входов означает больше строк выбора: мультиплексор 4-к-1 будет иметь 2 строки выбора, 8-к-1 — 3 и так далее (2 n входов требуют n строк выбора).

Думайте о мультиплексоре как о «цифровом коммутаторе». Строка выбора — это бросок на переключатель, она выбирает, какой из множества входов станет выходом.

Вот как можно сделать мультиплексор 2: 1 из логических вентилей. A и B — это два входа, X — это вход выбора, а Y — выход.

Вот как будет выглядеть таблица истинности для такой схемы:

| Выбрать вход (X) | Вход A | Вход B | Выход Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Время LogicBlock!

Что вам понадобится

- 2x блока AND

- 1x OR Блок

- 1x инверторный блок

- 1x разделительный блок

- 3x входных блока

- 1x кабель обратной связи

- 1x блок питания

Макет LogicBlocks

Следуйте схеме ниже, чтобы создать мультиплексор 2: 1 (Подсказка: обратите больше внимания, чем мы на сопоставление меток + и -!):

Нам нужно будет внутренне пометить каждый из входов.Вход селектора (X) — это одинокий вход, ведущий к вентилю НЕ. Остальные два входа — это наши A и B , которым вы можете присвоить произвольное имя.

Выход этого мультиплексора отображается желтым светодиодом на вентиле OR .

Эксперимент

Попробуйте этот порядок операций:

- Исходное состояние: установите для всех трех входов значение 0. На выходе должно быть 0.

- Переверните A на 1 .С выходом ничего не должно происходить, так как при установке переключателя в положение 0 вход B подается на выход.

- Переключите вход B на 1 . Наблюдайте за выходом и установите B обратно в 0. Выход должен соответствовать вашему переключению на B!

- Переключитесь на 1 . Выходные данные теперь должны следовать за входом A, и ему все равно, что установлено на B.

- Эта схема — комбинационная или последовательная? (Не позволяйте кабелю «Обратная связь» вводить вас в заблуждение!)

- Вы можете представить, как может выглядеть мультиплексор 4-к-1? Это потребовало бы удвоения входных линий — двух селекторов и четырех возможных входов.Вот схема (с цветовой кодировкой) для мультиплексора 4-к-1:

Для демультиплексирования 4-к-1 требуется четыре логических И с 3 входами, четыре НЕ и одно ИЛИ с 4 входами. Эта схема позволяет нам выбрать отправку A, B, C или D на выход X. X 0 и X 1 выполняют выбор.

- Как вы думаете, сколько шлюзов может потребоваться мультиплексору 8-к-1?

← Предыдущая страница

6. Защелка SR

Wikizero — Multiplexer

Эта статья о коммутации электроники.Для телекоммуникаций см. Мультиплексирование. Схема мультиплексора 2-к-1. Его можно приравнять к управляемому переключателю. Схема демультиплексора 1-2. Как и мультиплексор, его можно приравнять к управляемому переключателю.

В электронике мультиплексор (или мультиплексор ; иногда обозначается как мультиплексор ), также известный как селектор данных , представляет собой устройство, которое выбирает между несколькими аналоговыми или цифровыми входными сигналами и направляет их на один выход. линия.{n}} input имеет n {\ displaystyle n} строк выбора, которые используются для выбора, какую строку ввода отправить на вывод. [2] Мультиплексоры в основном используются для увеличения объема данных, которые могут быть отправлены по сети в течение определенного периода времени и полосы пропускания. [1] Мультиплексоры также могут использоваться для реализации булевых функций нескольких переменных.

Электронный мультиплексор позволяет нескольким сигналам совместно использовать одно устройство или ресурс, например, один аналого-цифровой преобразователь или одну среду передачи данных, вместо того, чтобы иметь одно устройство на каждый входной сигнал.

И наоборот, демультиплексор (или демультиплексор ) — это устройство, принимающее один вход и выбирающее сигналы выхода совместимого мультиплексора , который подключен к одному входу, и общей линии выбора. Мультиплексор часто используется с дополнительным демультиплексором на принимающей стороне. [1]

Электронный мультиплексор можно рассматривать как переключатель с несколькими входами и одним выходом, а демультиплексор — как переключатель с одним входом и несколькими выходами. [3] Схематическое обозначение мультиплексора представляет собой равнобедренную трапецию с более длинной параллельной стороной, содержащей входные контакты, и короткой параллельной стороной, содержащей выходной контакт. [4] На схеме справа показан мультиплексор 2: 1 слева и эквивалентный переключатель справа. Провод sel {\ displaystyle sel} соединяет желаемый вход с выходом.

Экономия затрат [править]

Основная функция мультиплексора: объединение нескольких входов в единый поток данных.На приемной стороне демультиплексор разделяет единый поток данных на несколько исходных сигналов.

Одно из применений мультиплексоров — это экономия подключений по одному каналу путем подключения одного выхода мультиплексора к одному входу демультиплексора. Изображение справа демонстрирует это преимущество. В этом случае стоимость реализации отдельных каналов для каждого источника данных выше, чем стоимость и неудобство предоставления функций мультиплексирования / демультиплексирования.

На принимающей стороне канала данных обычно требуется дополнительный демультиплексор , чтобы разбить единичный поток данных обратно на исходные потоки.В некоторых случаях удаленная система может иметь более широкие функциональные возможности, чем простой демультиплексор; и хотя демультиплексирование все еще происходит технически, оно никогда не может быть реализовано дискретно. Это было бы типично, когда: мультиплексор обслуживает несколько пользователей IP-сети; а затем подает непосредственно в маршрутизатор, который немедленно считывает содержимое всей ссылки в свой процессор маршрутизации; а затем выполняет демультиплексирование в памяти, откуда он будет преобразован непосредственно в разделы IP.

Часто мультиплексор и демультиплексор объединяются в одно оборудование, которое обычно называют «мультиплексором».Оба элемента схемы необходимы на обоих концах линии передачи, потому что большинство систем связи передают в обоих направлениях.

В аналоговой схеме мультиплексор — это особый тип аналогового переключателя, который соединяет один сигнал, выбранный из нескольких входов, с одним выходом.

Цифровые мультиплексоры [править]

В конструкции цифровых схем провода переключателя имеют цифровое значение. В случае мультиплексора 2: 1 логическое значение 0 будет подключать I0 {\ displaystyle \ scriptstyle I_ {0}} к выходу, а логическое значение 1 подключит I1 {\ displaystyle \ scriptstyle I_ {1 }} к выходу.В больших мультиплексорах количество выводов селектора равно ⌈log2 (n) ⌉ {\ displaystyle \ scriptstyle \ left \ lceil \ log _ {2} (n) \ right \ rceil}, где n {\ displaystyle \ scriptstyle n } — количество входов.

Например, для 9–16 входов потребуется не менее 4 контактов переключателя, а для 17–32 входов потребуется не менее 5 контактов переключателя. Двоичное значение, выраженное на этих контактах селектора, определяет выбранный входной контакт.

Мультиплексор 2 к 1 имеет логическое уравнение, где A {\ displaystyle \ scriptstyle A} и B {\ displaystyle \ scriptstyle B} — два входа, S0 {\ displaystyle \ scriptstyle S_ {0}} — селектор input, а Z {\ displaystyle \ scriptstyle Z} — это результат:

Multiplexer and De-Multiplexer

Мультиплексор и де-мультиплексор

В следующей статье мы подробно обсудим устройство и работу мультиплексора и демультиплексора.

Мультиплексор (MUX)

Операция отправки одного или нескольких аналоговых или цифровых сигналов по общей линии передачи в разное время или на разных скоростях называется мультиплексированием, а устройство, используемое для этого, известно как мультиплексор .

Мультиплексор , сокращенно «MUX», представляет собой комбинационную логическую схему, предназначенную для переключения одной из нескольких входных линий на единую общую выходную линию путем подачи управляющего сигнала.

Мультиплексоры

или MUX могут быть либо цифровыми схемами, сделанными из высокоскоростных логических вентилей, используемых для переключения цифровых или двоичных данных, либо они могут быть аналоговыми типами, использующими транзисторы, полевые МОП-транзисторы или реле для переключения одного из входов напряжения или тока на единственный выход.

Самый простой тип мультиплексора — это односторонний поворотный переключатель, как показано ниже:

Базовый переключатель мультиплексирования

Рис.1

Поворотный переключатель — это ручной переключатель, который можно использовать для выбора отдельных линий данных или сигналов, просто переводя его входы в положение «ВКЛ» или «ВЫКЛ».

В цифровой электронике мультиплексоры состоят из отдельных аналоговых переключателей, заключенных в единую ИС, по сравнению с переключателями «механического» типа, такими как обычные обычные переключатели и реле.

Как правило, выбор каждой входной линии в мультиплексоре контролируется дополнительным набором входов, называемых управляющими линиями , и в соответствии с двоичным состоянием этих управляющих входов, либо «ВЫСОКИЙ», либо «НИЗКИЙ», соответствующий вход данных подключен прямо на выход.

Обычно мультиплексор имеет четное число из 2 строк ввода данных N и количество «управляющих» входов, которое соответствует количеству входных данных.

Мы можем построить простой мультиплексор с 2 на 1 линию (2 к 1) из базовых логических вентилей NAND, как показано.

Конструкция мультиплексора с 2 входами

Рис.2

Рис.3

Вход A этой простой схемы мультиплексора 2-1 строк управляет тем, какой вход (I 0 или I 1 ) будет передан на выход Q.

Из таблицы истинности мы видим, что, когда вход выбора данных A имеет низкий уровень (логический 0), вход I 1 передает свои данные на выход, в то время как вход I 0 заблокирован.

Когда выбор данных A является ВЫСОКИМ (логическая 1), вход I 0 передается на Q, а вход I 0 блокируется.

В приведенном выше примере мультиплексор с 2 входами подключает один из двух 1-битных источников к общему выходу, создавая мультиплексор 2 в 1, и мы можем подтвердить это в следующем булевом выражении.

и для схемы мультиплексора с 2 входами выше, это можно упростить до:

Более крупные схемы мультиплексора могут быть реализованы с использованием меньших мультиплексоров 2 к 1 в качестве основных строительных блоков.

Итак, для мультиплексора с 4 входами нам потребуются две строки выбора данных, так как 2 2 = 4, следовательно, две линии управления данными будут давать схему с четырьмя входами.

Мультиплексор каналов 4 в 1

A 4-1 MUX с четырьмя входами: A, B, C, D и двумя линиями выбора данных a и b показан ниже:

Рис.4

Логическое выражение для этого мультиплексора , приведенного выше, с входами от A до D и строками выбора данных a, b, имеет вид:

Q = abA + abB + abC + abD

В этом примере в любой момент времени только ОДИН из четырех аналоговых переключателей замкнут, соединяя только одну из входных линий A — D с одиночным выходом в Q.

То, какой переключатель замкнут, зависит от входного кода адресации в строках «a» и «b», поэтому для этого примера, чтобы выбрать вход B для выхода на Q, адрес двоичного входа должен быть «a» = логический «1» и «b» = логический «0».

Выбор входной линии мультиплексора

Выбор данных через мультиплексор может отображаться как функция битов выбора данных, как показано ниже:

Рис.5

Добавление дополнительных линий управления позволит мультиплексору управлять большим количеством входов, но каждая конфигурация линии управления будет подключать только ОДИН вход к выходу.

4-1 MUX с использованием логических вентилей

Реализация логического выражения мультиплексора 4-1 с использованием семи отдельных вентилей, состоящих из вентилей И, ИЛИ и НЕ, показана ниже:

Рис.6

Символ мультиплексора

Рис.7

Демультиплексор

Демультиплексор или сокращенно «демультиплексор» — полная противоположность мультиплексора.

Демультиплексор принимает одну единственную строку входных данных и затем переключает ее на любую из ряда отдельных выходных линий по одной за раз.

Демультиплексор преобразует сигнал последовательных данных на входе в параллельные данные на своих выходных линиях, как показано ниже.

Демультиплексор с 1 в 4 канала

Рис.8

Рис.9

Логическое выражение для этого демультиплексора от 1 до 4 выше с выходами от A до D и строками выбора данных a, b имеет следующий вид:

F = abA + abB + abC + abD

Выбор выходной линии демультиплексора

Функция демультиплексора заключается в переключении одной линии ввода общих данных на любую из 4 линий выходных данных от A до D в нашем примере выше.

Как и в случае с мультиплексором, отдельные твердотельные переключатели выбираются адресным кодом двоичного входа на выводах выбора выхода «a» и «b», как показано ниже:

Рис.