Синтез комбинационных схем. Понятие логического элемента. Типовые логические элементы и их обозначения на функциональных схемах. Схема логического элемента и

Элементная база различных логик: схемы, ТТЛ, ТТЛШ, КМОП

Для конкретной серии микросхем характерно использование типового электронного узла — базового логического элемента. Этот элемент является основой построения самых разнообразных цифровых электронных устройств.

Для конкретной серии микросхем характерно использование типового электронного узла — базового логического элемента. Этот элемент является основой построения самых разнообразных цифровых электронных устройств.

Ниже рассмотрим особенности базовых логических элементов различных логик.

Элементы транзисторно-транзисторной логики

Характерной особенностью ТТЛ является использование многоэмиттерных транзисторов. Эти транзисторы сконструированы таким образом, что отдельные эмиттеры не оказывают влияния друг на друга. Каждому эмиттеру соответствует свой p-n-переход. В первом приближении многоэмиттерный транзисторможет моделироваться схемой на диодах (см. пунктир на рис. 3.27).

Упрощенная схема ТТЛ-элемента приведена на рис. 3.27. При мысленной замене многоэмиттерного транзистора диодами получаем элемент диодно-транзисторной логики «И-НЕ». Из анализа схемы можно сделать вывод, что если на один из входов или на оба входа подать низкий уровень напряжения, то ток базы транзистора Т2 будет равен нулю, и на коллекторе транзистора Т2 будет высокий уровень напряжения. Если на оба входа подать высокий уровень напряжения, то через базу Т2 транзистора будет протекать большой базовый ток и на коллекторе транзистора Т2 будет низкий уровень напряжения, т. е. данный элемент реализует функцию И-НЕ:

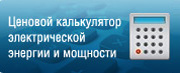

uвых= u1· u2. Базовый элемент ТТЛ содержит многоэмиттерный транзистор, выполняющий логическую операцию И, и сложный инвертор (рис. 3.28).  Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор Т2 закрыт, а следовательно, закрыт и транзистор Т4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор Т2 открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора Т4 и запиранию транзистора Т3, т. е. реализуется функция И-НЕ.

Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор Т2 закрыт, а следовательно, закрыт и транзистор Т4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор Т2 открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора Т4 и запиранию транзистора Т3, т. е. реализуется функция И-НЕ.

Для увеличения быстродействия элементов ТТЛ используются транзисторы с диодами Шоттки (транзисторы Шоттки).

Базовый логический элемент ТТЛШ (на примере серии К555)

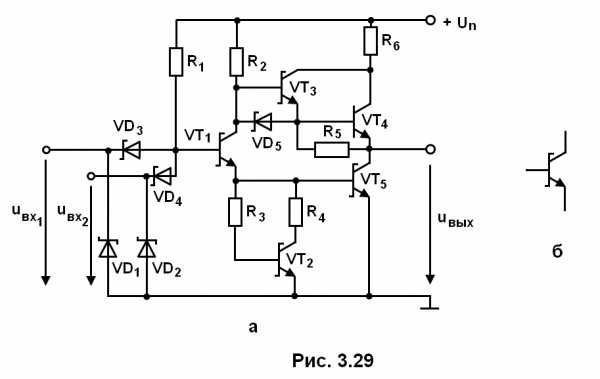

В качестве базового элемента серии микросхем К555 использован элемент И-НЕ. На рис. 3.29, а изображена схема этого элемента, а условное графическое обозначение транзистора Шоттки приведено на рис. 3.29, б.  Такой транзистор эквивалентен рассмотренной выше паре из обычного транзистора и диода Шоттки. ТранзисторVT4 — обычный биполярный транзистор.

Такой транзистор эквивалентен рассмотренной выше паре из обычного транзистора и диода Шоттки. ТранзисторVT4 — обычный биполярный транзистор.

Если оба входных напряжения uвх1и uвх2 имеют высокий уровень, то диодыVD3 и VD4 закрыты, транзисторы VT1,VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона).

Микросхемы ТТЛШ

Микросхемы ТТЛШ серии К555 характеризуются следующими параметрами:

● напряжение питания +5 В;

● выходное напряжение низкого уровня — не более 0,4 В;

● выходное напряжение высокого уровня — не менее 2,5 В;

● помехоустойчивость — не менее 0,3 В;

● среднее время задержки распространения сигнала — 20 нс;

● максимальная рабочая частота — 25 МГц.

Микросхемы ТТЛШ обычно совместимы по логическим уровням, помехоустойчивости и напряжению питания с микросхемами ТТЛ. Время задержки распространения сигнала элементов ТТЛШ в среднем в два раза меньше по сравнению с аналогичными элементами ТТЛ.

Особенности других логик

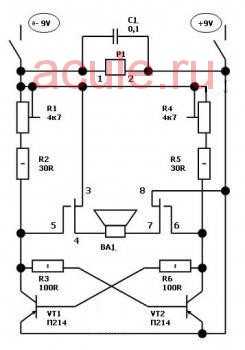

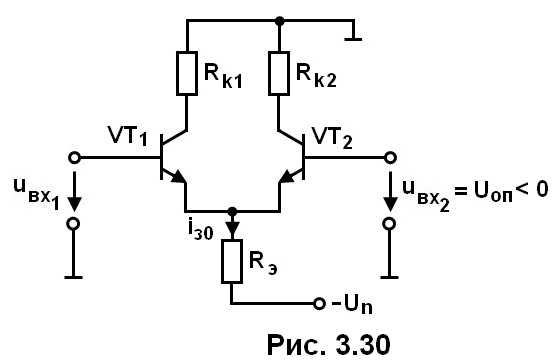

Основой базового логического элемента ЭСЛ является токовый ключ. Схема токового ключа (рис. 3.30) подобна схеме дифференциального усилителя.  Необходимо обратить внимание на то, что микросхемы ЭСЛ питаются отрицательным напряжением (к примеру, −4,5 В для серии К1500). На базу транзистора VT2 подано отрицательное постоянное опорное напряжение Uоп. Изменение входного напряжения uвх1 приводит к перераспределению постоянного тока iэ0, заданного сопротивлением Rэ между транзисторами, что имеет следствием изменение напряжений на их коллекторах. Транзисторы не входят в режим насыщения, и это является одной из причин высокого быстродействия элементов ЭСЛ.

Необходимо обратить внимание на то, что микросхемы ЭСЛ питаются отрицательным напряжением (к примеру, −4,5 В для серии К1500). На базу транзистора VT2 подано отрицательное постоянное опорное напряжение Uоп. Изменение входного напряжения uвх1 приводит к перераспределению постоянного тока iэ0, заданного сопротивлением Rэ между транзисторами, что имеет следствием изменение напряжений на их коллекторах. Транзисторы не входят в режим насыщения, и это является одной из причин высокого быстродействия элементов ЭСЛ.

Микросхемы серий 100, 500 имеют следующие параметры:

● напряжение питания −5,2 В;

● потребляемая мощность — 100 мВт;

● коэффициент разветвления по выходу — 15;

● задержка распространения сигнала — 2,9 нс.

В микросхемах n-МОП и p-МОП используются ключи соответственно на МОП-транзисторах с n-каналом и динамической нагрузкой (рассмотрены выше) и на МОП-транзисторах с p-каналом.

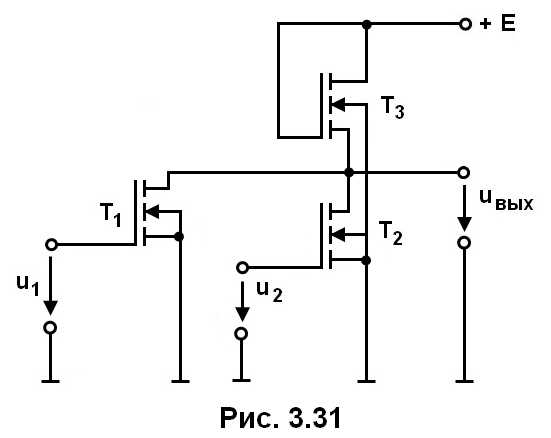

В качестве примера рассмотрим элемент логики n-МОП, реализующий функцию ИЛИ-НЕ (рис. 3.31).

Он состоит из нагрузочного транзистора Т3 и двух управляющих транзисторов Т1 и Т2. Если оба транзистора Т1 и Т2 закрыты, то на выходе устанавливается высокий уровень напряжения. Если одно или оба напряжения u1и u2 имеют высокий уровень, то открывается один или оба транзистора Т1 и Т2 и на выходе устанавливается низкий уровень напряжения, т. е. реализуется функция uвых= u1 + u2.

Для исключения потребления мощности логическим элементом в статическом состоянии используются комплементарные МДП — логические элементы (КМДП или КМОП-логика). В микросхемах КМОП используются комплементарные ключи на МОП-транзисторах. Они отличаются высокой помехоустойчивостью. Логика КМОП является очень перспективной. Рассмотренный ранее комплементарный ключ фактически является элементом НЕ (инвертором).

КМОП — логический элемент

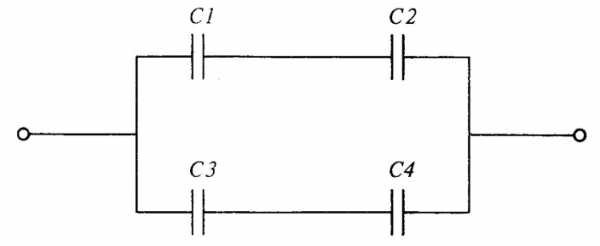

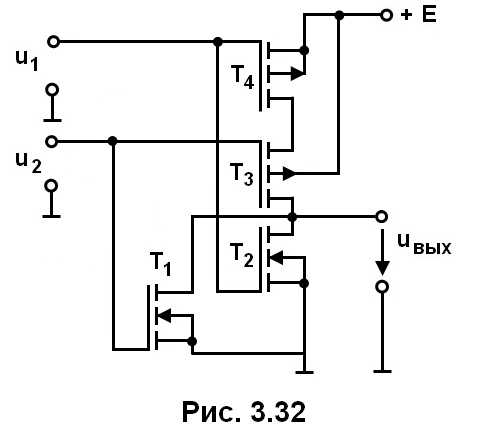

Рассмотрим КМОП — логический элемент, реализующий функцию ИЛИ-НЕ (рис. 3.32).

Если входные напряжения имеют низкие уровни (u1и u2меньше порогового напряжения n-МОП-транзистора Uзи.порог.n), то транзисторы Т1 и Т2 закрыты, транзисторы Т3 и Т4 открыты и выходное напряжение имеет высокий уровень. Если одно или оба входных напряжения u1и u2 имеют высокий уровень, превышающий Uзи.порог.n, то открывается один или оба транзистора Т1 и Т2, а между истоком и затвором одного или обоих транзисторов Т3 и Т4 устанавливается низкое напряжение, что приводит к запиранию одного или обоих транзисторов Т3 и Т4, а следовательно, на выходе устанавливается низкое напряжение. Таким образом, этот элемент реализует функцию uвых= u1+u2 и потребляет мощность от источника питания лишь в короткие промежутки времени, когда происходит его переключение.

Интегральная инжекционная логика (ИИЛ или И2Л) построена на использовании биполярных транзисторов и применении оригинальных схемотехнических и технологических решений. Для нее характерно очень экономичное использование площади кристалла полупроводника. Элементы И2Л могут быть реализованы только в интегральном исполнении и не имеют аналогов в дискретной схемотехнике.  Структура такого элемента и его эквивалентная схема приведены на рис. 3.33, из которого видно, что транзистор T1 (p-n-p) расположен горизонтально, а многоколлекторный транзистор Т2 (n-p n) расположен вертикально. Транзистор T1 выполняет роль инжектора, обеспечивающего поступление дырок из эмиттера транзистора T1 (при подаче на него положительного напряжения через ограничивающий резистор) в базу транзистора Т2. Если u1 соответствует логическому «0», то инжекционный ток не протекает по базе многоколлекторного транзистора Т2 и токи в цепях коллекторов транзистора Т2 не протекают, т. е. на выходах транзистора Т2 устанавливаются логические «1». При напряжении u1 соответствующем логической «1», инжекционный ток протекает по базе транзистора Т2 и на выходах транзистора Т2 — логические нули.

Структура такого элемента и его эквивалентная схема приведены на рис. 3.33, из которого видно, что транзистор T1 (p-n-p) расположен горизонтально, а многоколлекторный транзистор Т2 (n-p n) расположен вертикально. Транзистор T1 выполняет роль инжектора, обеспечивающего поступление дырок из эмиттера транзистора T1 (при подаче на него положительного напряжения через ограничивающий резистор) в базу транзистора Т2. Если u1 соответствует логическому «0», то инжекционный ток не протекает по базе многоколлекторного транзистора Т2 и токи в цепях коллекторов транзистора Т2 не протекают, т. е. на выходах транзистора Т2 устанавливаются логические «1». При напряжении u1 соответствующем логической «1», инжекционный ток протекает по базе транзистора Т2 и на выходах транзистора Т2 — логические нули.

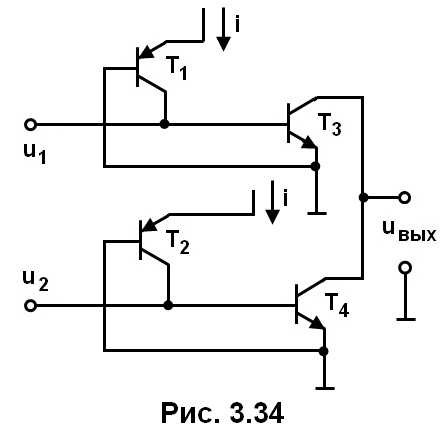

Рассмотрим реализацию элемента ИЛИ-НЕ на основе элемента, представленного на рис. 3.34 (для упрощения другие коллекторы многоколлекторных транзисторов Т3 и Т4 на рисунке не показаны). Когда на один или оба входа подается логический сигнал «1», то напряжение uвых соответствует логическому нулю. Если на обоих входах логические сигналы «0», то напряжение uвых соответствует логической единице.  Логика на основе полупроводника из арсенида галлия GaAs характеризуется наиболее высоким быстродействием, что является следствием высокой подвижности электронов (в 3…6 раз больше по сравнению с кремнием). Микросхемы на основе GaAs могут работать на частотах порядка 10 ГГц и более.

Логика на основе полупроводника из арсенида галлия GaAs характеризуется наиболее высоким быстродействием, что является следствием высокой подвижности электронов (в 3…6 раз больше по сравнению с кремнием). Микросхемы на основе GaAs могут работать на частотах порядка 10 ГГц и более.

pue8.ru

НОУ ИНТУИТ | Лекция | Реализация логических элементов

Аннотация: Рассматривается различные технологии реализации логических элементов.

Логические элементы транзисторно-транзисторной логики

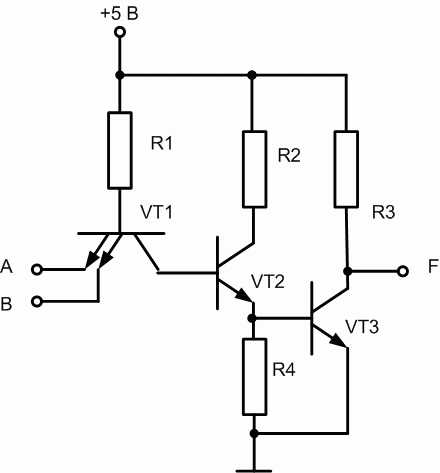

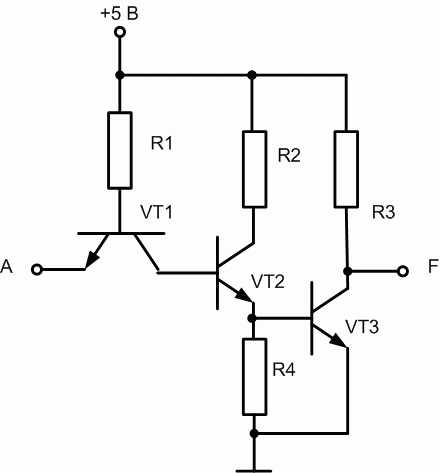

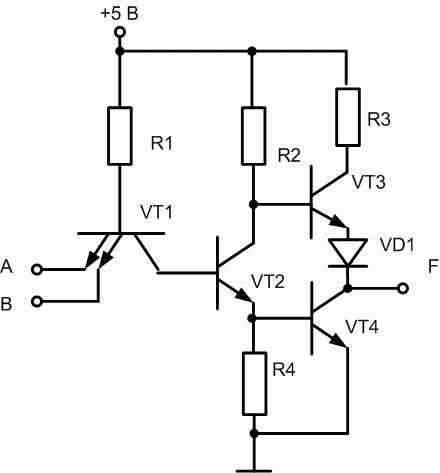

Схемы транзисторно-транзисторной логики (ТТЛ) базируются на биполярных транзисторах npn-структуры. Базовым элементом (рис. 16.1) данной технологии является схема И-НЕ. Логическое умножение осуществляется за счет свойств многоэмиттерного транзистора VT1 [1]. При подаче хотя бы одного логического нуля на эмиттеры этого транзистора замыкается цепь: +5 В, сопротивление R1, переход база-эмиттер, земля на входе. При этом транзисторы VT2 и VT3 остаются закрытыми. Поэтому выходная цепь не замкнута, падения напряжения в ней нет, следовательно, в точке F на выходе схемы будет потенциал источника питания, т.е. логическая единица. Выполняется правило И-НЕ [2]: при подаче хотя бы одного нуля на выходе схемы получили логическую единицу.

Рис. 16.1. Базовый элемент И-НЕ на ТТЛ

Рис. 16.1. Базовый элемент И-НЕ на ТТЛПри подаче логической единицы на все входы схемы замыкается цепь: +5 В, сопротивление R2, транзистор VT2, сопротивление R3 , земля. Следовательно, на базу выходного транзистора VT3 подается потенциал, достаточный для его открытия (соответствует падению напряжения на сопротивлении R3). Через открытый транзистор VT3 замыкается буферная цепь: +5 В, сопротивление R4, транзистор VT3, земля. Следовательно, на выходе F будет потенциал, соответствующий падению напряжения на открытом транзисторе VT3, т.е. 0.4 В. Таким образом, F=0.

На рис. 16.2 представлен логический элемент ИЛИ-НЕ. Логическое сложение осуществляется за счет монтажного соединения транзисторов VT3 и VT4. Замыкание буферной цепи (состояние F=0 ) в этом случае возможно при замыкании хотя бы одной из цепей, проходящих через сопротивления R2 и R3. Эти цепи замыкаются в том случае, если на входы подается хотя бы одна логическая единица. Таким образом, выполняется правило ИЛИ-НЕ [2]: при подаче хотя бы одной единицы на выходе схемы получим логический ноль.

При замене в схеме И-НЕ многоэмиттерного транзистора VT1 на одноэмиттерный получается инвертор (рис. 16.3).

Рис. 16.3. Логический элемент НЕ на ТТЛ

Рис. 16.3. Логический элемент НЕ на ТТЛБуферная часть схем логических элементов ТТЛ-технологии может быть реализована по-разному. В частности, резистор в буферной части может быть вынесен за пределы интегральной схемы, при этом существенно уменьшаются потери и нагрев кристалла. Такие схемы называются схемами "с открытым коллектором ". Пример такой схемы приведен на рис. 16.4.

Рис. 16.4. Базовый элемент И-НЕ на ТТЛ с открытым коллектором

Рис. 16.4. Базовый элемент И-НЕ на ТТЛ с открытым коллекторомВ схемах с активной нагрузкой (рис. 16.5) состояние буферной цепи определяется состоянием не одного, а двух транзисторов.

Рис. 16.5. Базовый элемент И-НЕ на ТТЛ с активной нагрузкой

Рис. 16.5. Базовый элемент И-НЕ на ТТЛ с активной нагрузкойБуферные схемы на три состояния (первые два – логический 0 и логическая 1 ) имеют помимо информационных, разрешающий вход Е (рис. 16.6). При Е=1 диод VD2 подключен на обратное напряжение, поэтому дополнительная цепь, включающая в себя диод VD2 и вход Е, разомкнута и не влияет на работу логического элемента. Таким образом, осуществляется "разрешение" работы элемента. При отсутствии такового разрешения Е=0. Диод VD2 оказывается подключенным на прямое напряжение, замыкается цепь + 5 В, сопротивление R2, открытый диод VD2, земля на входе E. Следовательно, на базу транзистора VT3 в буферной части схемы подается потенциал, соответствующий падению напряжения на открытом диоде, т.е. 0.2 В. При таких условиях данный транзистор закрыт, поэтому выход F оказывается отключенным от источника питания. Кроме того, независимо от состояния информационных входов A и B, замкнется входная цепь +5 В, сопротивление R1, переход база-эмиттер транзистора VT1, земля на входе E. Поэтому, как было описано выше, транзисторы VT2 и VT4 будут закрыты. Вследствие закрытия VT4 выход F будет отключен также и от земли. Таким образом, схема будет не в нулевом и не в единичном, а в "третьем" состоянии, которое называется состоянием высокого сопротивления, Z-состоянием, высокоимпедансным состоянием. Все перечисленные термины обозначают одно и то же: выход схемы отключен и от источника питания, и от земли.

Рис. 16.6. Базовый элемент И-НЕ на ТТЛ с выходом на три состояния

Рис. 16.6. Базовый элемент И-НЕ на ТТЛ с выходом на три состоянияЛогические элементы nМОП-технологии

Схемы nМОП-технологии базируются на полевых (МОП) транзисторах с индуцированным каналом n-типа. Базовым элементом (рис. П16.7) данной технологии является схема И-НЕ. Логическое умножение осуществляется за счет последовательного соединения каналов транзисторов VT1 и VT2. Канал между истоком и стоком в nМОП-транзисторе индуцируется в том случае, когда на затвор (вход схемы) подается положительный относительно подложки потенциал. Цепь от +5 В до земли замкнется только в одном случае, когда A=B=1, поскольку в этом случае оба транзистора открываются и образуется единый канал, замыкающий цепь.

Рис. 16.7. Логический элемент И-НЕ nМОП-технологииФункция ИЛИ-НЕ осуществляется за счет параллельного соединения таких транзисторов (рис. 16.8): при подаче хотя бы на один вход единицы индуцируется канал в соответствующем транзисторе и замыкается цепь от +5 В до земли. Следовательно, на выходе будет потенциал, соответствующий падению напряжения в канале транзистора, т.е. 0,2 В, при этом F=0.

Рис. 16.8. Логический элемент ИЛИ-НЕ nМОП-технологии

Рис. 16.8. Логический элемент ИЛИ-НЕ nМОП-технологииСхема инвертора (рис. 16.9) строится на базе одного транзистора.

Рис. 16.9. Логический элемент НЕ nМОП-технологииwww.intuit.ru

Логические элементы и способы построения логических элементов

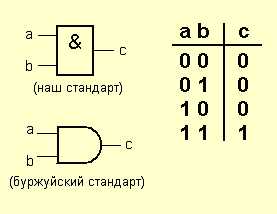

Элемент «И» (AND)

Иначе его называют «конъюнктор». Таблицы истинности широко применяются в цифровой технике для описания работы логических схем.

Вот так выглядит элемент «И» и его таблица истинности:

Поскольку нам придется общаться как с русской, так и с буржуйской тех. документацией, я буду приводить условные графические обозначения (УГО) элементов и по нашим и по не нашим стандартам.

Смотрим таблицу истинности, и проясняем в мозгу принцип. Понять его не сложно: единица на выходе элемента «И» возникает только тогда, когда на оба входа поданы единицы. Это объясняет название элемента: единицы должны быть И на одном, И на другом входе.

Если посмотреть чуток иначе, то можно сказать так: на выходе элемента «И» будет ноль в том случае, если хотя бы на один из его входов подан ноль. Запоминаем. Идем дальше.

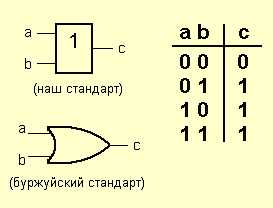

Элемент «ИЛИ» (OR)

По другому, его зовут «дизъюнктор».

Любуемся:

Опять же, название говорит само за себя.

На выходе возникает единица, когда на один ИЛИ на другой ИЛИ на оба сразу входа подана единица. Этот элемент можно назвать также элементом «И» для негативной логики: ноль на его выходе бывает только в том случае, если и на один и на второй вход поданы нули.

Едем дальше. Дальше у нас очень простенький, но очень необходимый элемент.

Элемент «НЕ» (NOT)

Чаще, его называют «инвертор».

Надо чего-нибудь говорить по поводу его работы?

Ну тогда поехали дальше. Следующие два элемента получаются путем установки инвертора на выход элементов «И» и «ИЛИ».

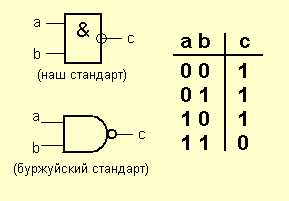

Элемент «И-НЕ» (NAND)

Элемент И-НЕ работает точно так же как «И», только выходной сигнал полностью противоположен. Там где у элемента «И» на выходе должен быть «0», у элемента «И-НЕ» - единица. И наоборот. Э то легко понять по эквивалентной схеме элемента:

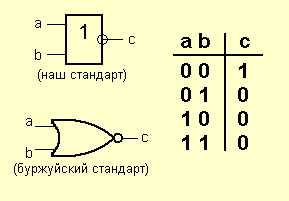

Элемент «ИЛИ-НЕ» (NOR)

Та же история – элемент «ИЛИ» с инвертором на выходе.

Следующий товарищ устроен несколько хитрее:

Элемент «Исключающее ИЛИ» (XOR)

Он вот такой:

Операция, которую он выполняет, часто называют «сложение по модулю 2». На самом деле, на этих элементах строятся цифровые сумматоры.

Смотрим таблицу истинности. Когда на выходе единицы? Правильно: когда на входах разные сигналы. На одном – 1, на другом – 0. Вот такой он хитрый.

Эквивалентная схема примерно такая:

Ее запоминать не обязательно.

Собственно, это и есть основные логические элементы. На их основе строятся абсолютно любые цифровые микросхемы. Даже ваш любимый Пентиум 4.

Далее мы позанудствуем о том, как синтезировать цифровую схему, имея ее таблицу истинности. Это совсем несложно, а знать надо, ибо пригодится (еще как пригодится) нам в дальнейшем.

Ну и напоследок – несколько микросхем, внутри которых содержатся цифровые элементы. Около выводов элементов обозначены номера соответствующих ног микросхемы. Все микросхемы, перечисленные здесь, имеют 14 ног. Питание подается на ножки 7 (-) и 14 (+). Напряжение питания – смотри в таблице в предыдущем параграфе.

lab201.jimdo.com

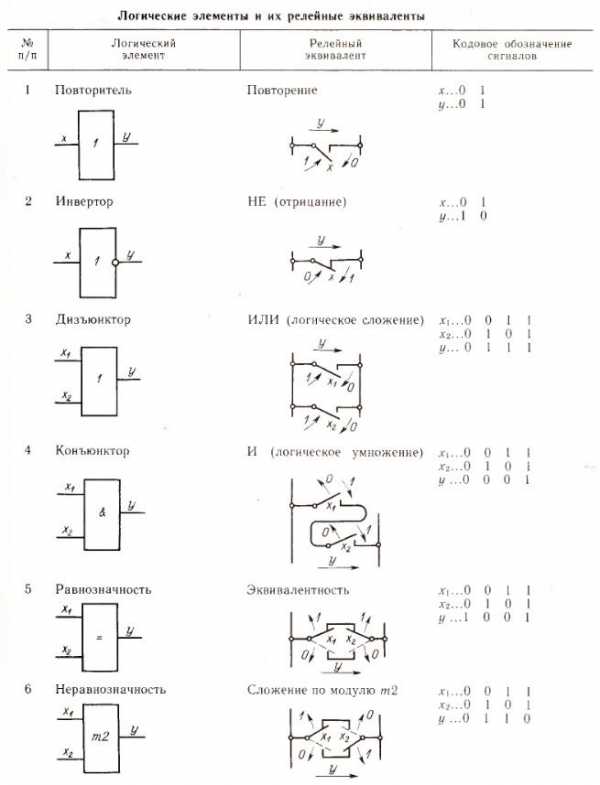

Логические элементы и их релейные эквиваленты

С помощью логических элементов довольно легко реализуются функции алгебры логики, которая является костяком устройств автоматики и вычислительных машин. Логические элементы могут реализовываться огромным количеством способов в зависимости от надобности и состоять из полупроводниковых, релейных, интегральных, пневматических и других элементов и схем.

Между величинами, входящими и выходящими из логического элемента, существует определенная зависимость, которая называется функциональной и обозначается как y = f(x) для устройств с одной переменной и как y = f(x1, x2) для устройств с двумя переменными величинами. В этой записи Х называют независимую переменную или аргумент, а Y – зависимая переменная, так как ее значение напрямую зависит от значения аргумента Х.

Ниже показана таблица логических элементов и эквивалентных им положений контактов реле:

Функция повторения

Реализуется логическим элементом повторителем (пункт 1 в таблице). Повторитель можно сравнить с нормально открытым контактом реле. При открытом контакте Х=0 и, соответственно Y=0, то есть цепь находится в непроводящем состоянии, а при закрытом наоборот Х=1 и Y=1, то есть цепь находится в проводящем состоянии.

Функция отрицания

Реализует данную функцию логический элемент НЕ или как его часто называют – инвертор (пункт 2 в таблице). Его сравнивают с нормально закрытым контактом реле, когда при отсутствии напряжения на катушке управления (Х=0) его контакт находится в проводящем состоянии (Y=1). При подаче напряжения на катушку (Х=1) контакт размыкается и разрывает цепь (Y=0).

Функция логического сложения

В схемотехнике носит название дизъюнкция или функция ИЛИ (пункт 3 в таблице). Реализуема эта функция логическим элементом дизъюнктором. Суть данной операции заключается в логическом суммировании входных сигналов X для получения результирующего сигнала на выходе Y. Описывается данная зависимость простой формулой X1 + X2 = Y. Вот примеры – 0+0=1, 1+0=1,0+1=1,1+1=1. На примере обычного реле – это два параллельно подключенных нормально разомкнутых контакта. Если один контакт разомкнут, то проводимость цепи обеспечит второй, замкнутый контакт. Для того что бы цепь оказалась разорванной, необходимо разомкнуть оба контакта.

Функция логического умножения

В схемотехнике носит название конъюнкция или функция И (пункт 4 в таблице). Реализует ее специальный логический элемент – конъюктор. Данная функция – логическое перемножение сигналов:

Если сравнить с реле – то это два последовательно включенные нормально открытые контакты. А при таком подключении контактов реле проводимость можно получить только в случае, когда оба контакта замкнуты.

Функция равнозначности

Имеет следующий вид — X1≡X2 = Y или в виде логических символов: 0≡0 =1; 1≡0 = 0; 0≡1 = 0; 1≡1 = 1.

Значения 1 будет только при условии, что X1 = X2. Эквивалентом в релейной схеме будет два последовательно включенных переключающихся контакта (пункт 5 в таблице).

Функция неравнозначности

Противоположная функции равнозначности (пункт 6 в таблице) и часто носит название функции сложности по модулю m2:

elenergi.ru

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Элементы математической логики - логические элементы. Цифровые микросхемы предназначены для выполнения определенных логических действий над входными сигналами. Если, например, на выходе цифровой микросхемы должно появиться напряжение высокого уровня в том случае, если напряжение высокого уровня присутствует хотя бы на одном из выходов, то говорят, что данная микросхема выполняет логическую операцию ИЛИ (логическое сложение). Если же логический сигнал на выходе микросхемы должен быть равен произведению логических сигналов на входах микросхемы, то говорят об операции логического умножения. Существует множество других правил обработки сигналов в цифровых микросхемах. Есть даже специальная область математики, которая исследует эти законы, – булева алгебра (по имени английского математика Дж. Буля). Вот почему цифровые микросхемы называют еще и логическими.В основу работы цифровых микросхем положена двоичная система счисления. В отличие от всем нам знакомой десятичной системы, имеющей десять цифр, двоичная система опирается лишь на две цифры: 0 и 1.

Двоичная система счисления используется в большинстве современных цифровых машин. Действия над числами двоичной системы счисления могут осуществлять простейшие логические элементы или их объединения. Логический элемент И имеет два входа и один выход. В верхней части прямоугольника стоит знак & (амперсант), который обозначает операцию объединения, перемножения. Это значит, что напряжение высокого уровня на выходе присутствует в том, и только в том случае, если на обоих входах также напряжения высокого уровня. Это поясняется таблицей истинности. Логический элемент ИЛИ имеет два входа и один выход. Если хотя бы на одном из входов есть напряжение высокого уровня, такое же напряжение будет и на выходе.

Логический элемент имеет один вход и один выход. Если на вход подать напряжение высокого уровня, то на выходе установится напряжение низкого уровня, и наоборот, т.е. говорят, что входной сигнал инвертируется элементом.Одним из наиболее широко применяемых радиолюбителями в своих конструкциях является логический элемент 2И-НЕ. Он предназначен для выполнения логического умножения с отрицанием. Если подавать входной сигнал на соединенные вместе входы, то он будет работать как инвертор. С помощью двух логических элементов 2И-НЕ можно производить операцию логического умножения, а с помощью трех логических элементов – операцию логического сложения.

Видно, что с помощью элемента 2И-НЕ можно реализовать любую логическую операцию. В предлагаемом стенде размещены пять блоков, каждый из которых иллюстрирует работу одного из логических элементов. Блоки подключаются к источнику питания индивидуально с помощью переключателя. Причем в нижней части схемы каждого блока загорается светодиод, показывающий работу этой схемы. Таким образом, переводя переключатель их одного положения в другое можно демонстрировать работу элементов: «И»; «ИЛИ»; «НЕ»; «2И – НЕ»; «2ИЛИ – НЕ». Каждый блок имеет условное графическое обозначение, электрический аналог, временные диаграммы, таблицу истинности.

Поделитесь полезными схемами| МОЩНЫЙ БЕСТРАНСФОРМАТОРНЫЙ ПРЕОБРАЗОВАТЕЛЬ Такой преобразователь напряжения может быть использован для маломощных гаусс-пушек и т.п. Преобразователь не имеет импульсного трансформатора, что резко уменьшает размеры печатной платы. |

| СХЕМА ТРАНСФОРМАТОРА Рассмотрим типовую схему электронного трансформатора и варианты его подключения в сеть. |

| МЯГКИЙ ПУСК Схема устройства так называемого "мягкого старта" - токоограничение потребителя при первых секундах включения в сеть 220В. |

samodelnie.ru

Синтез комбинационных схем. Понятие логического элемента. Типовые логические элементы и их обозначения на функциональных схемах.

Определение: как правило ,под логическим элементом понимается комбинационная схема ,реализующая некоторую элементарную булеву функцию.

Любой логический элемент характеризуется :

Наличием одного или нескольких входов на которые подаются входные сигналы( входные переменные).

Наличием выхода ,на котором формируется выходной сигнал

(выходная переменная).

Определенной функцией ,которая отображает зависимость выходного сигнала от входных.

К основным типам логических элементов относятся:

Инвертор( НЕ)

Дизъюнктор (ИЛИ)

Конъюнктор (И)

Дизъюнктор с отрицанием (ИЛИ - НЕ)

Конъюнктор с отрицанием (И - НЕ)

Исключительное ИЛИ

(единичный сигнал на выходе имеет место в том и только том случае если на

одном и только одном входе присутствует единичный сигнал)

Сумматор по модулю 2

1)Элементы 1,2,3 образуют булев базис.

2)Элементы 1 и 2 или 1 и 3 образует сокращенный(неполный)

булев базис.

3)Элементы 4 или 5 образуют универсальный базис.

4)Элементы 3 и 7 образуют базис Жегалкина.

Функции элементов 6 и 7 совпадают при наличии только двух входов.

Понятие двоичного сигнала. Способы его кодирования.

В связи с использованием двух значений логики в логических схемах как входные, так и выходные сигналы в этих схемах представляются с помощью так называемого двоичного сигнала - особенностью которого является наличие двух четко различимых уровней, отождествляемых с нулем и единицей.

В зависимости от того ,какой уровень сигнала сопоставляется с логическим нулем а какой с логической единицей различают два способа кодирования двоичных сигналов:

1)Позитивное кодирование (положительное)

высший уровень сигнала - 1 ,низший - 0

2)Негативное кодирование (отрицательное)

высший уровень сигнала - 0 ,низший - 1

При изменении способа кодирования двоичного сигнала функция одной и той же электронной схемы ,реализующей некоторый логический элемент меняется на противоположную.

Понятие логической системы. Типы логических систем.

Логическая схема представляет собой совокупность логических элементов и связей между ними.

Соединения логических элементов в рамках единой логической системы должны удовлетворять следующим правилам:

1)К любому входу логического элемента могут быть подключены:

a) выход любого другого логического элемента( в частном случае ,того же самого)

б) входной сигнал (входная переменная)

в) логическая константа(0 или 1)

В реальных электронных схемах подача логической константы на вход элемента реализуется либо заземлением либо подключением этого входа обязательно через резистор к шине питания.

2)Выход любого логического элемента схемы может быть подключен к входу другого логического элемента или представлять собой выходной сигнал схемы .В частном случае возможна комбинация того и другого.

Логические схемы разделяются на два типа :

1)Комбинационные

2)Последовательносные

В комбинационных схемах значение выходного сигнала в любой момент времени зависит только от комбинации входных сигналов (в этот же момент времени с учетом задержки распространения сигнала по элементам схемы)

С учетом этой задержки значение выходного сигнала по времени запаздывает на время задержки по сравнению с моментом изменения входных сигналов.

Функционирование комбинационной схемы может быть описано булевой функцией, отражающей зависимость выходного сигнала схемы, как функции от входных сигналов , как аргумент этой функции.

Для комбинационных схем с несколькими выходами эта зависимость отражается системой булевых функций.

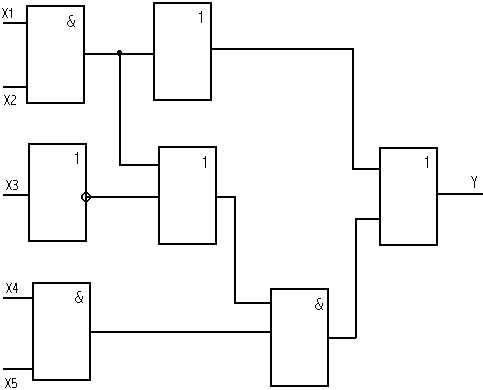

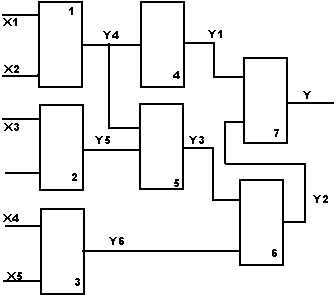

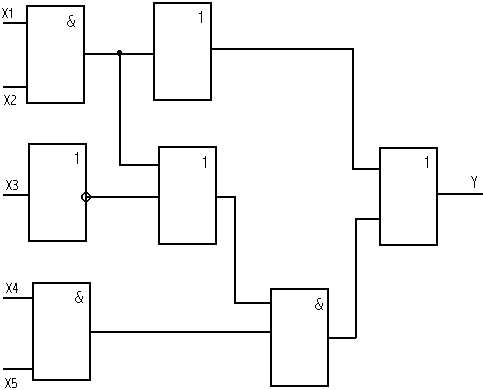

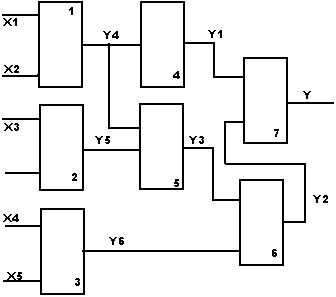

Пример комбинационной схемы на элементах булева базиса :

В последовательносных схемах выходные сигналы в любой момент времени зависят не только от комбинации входных сигналов в данный момент времени ,но и от предыстории их изменения ,то есть от последовательности входных сигналов во времени. Как правило последовательносные схемы характеризуются некоторым внутренним строением ,от которого зависит значение выходного сигнала(ов).

Внутреннее состояние такой схемы сохраняется на запоминающих элементах (триггерах) ,в связи с чем ,схемы этого типа называются схемами с памятью.

В общем случае поседовательносная схема представляет собой некоторый цифровой автомат.

Пример последовательносной схемы: (универсальный базис И-НЕ)

Последовательносные схемы характеризуются наличием так называемых петель ,по которым выход некоторого элемента соединяется со входом этого же самого элемента (через другие элементы схемы).

Основные параметры комбинационной схемы.

Основными параметрами комбинационных схем (КС) является стоимость и быстродействие ,как правило при построении абстрактных КС не привязанных к конкретной системе элементов цена схемы определяется в смысле Квайна. Быстродействие схемы ,как правило оценивается задержкой распространения сигналов от входов схемы к ее выходу. Для абстрактных КС эту задержку принято считать в виде : Т=кt ,t-задержка на одном логическом элементе, к - максимальное количество логических элементов ,через которые проходит сигнал от входов к выходу.

Как правило задержка схемы сопоставляется с числом уровней этой схемы. Для этой цели все элементы схемы распределяются по уровням. Уровень элемента ,на выходе которого формируется выходной сигнал схемы совпадает с количеством уровней схема и следовательно с ее задержкой.

Для приведенной схемы элементы 1,2,3 относятся к первому уровню.

Элементы 4,5 ко второму уровню.

Элемент 6 к третьему уровню.

Элемент 7 к четвертому уровню.

studfiles.net

Синтез комбинационных схем. Понятие логического элемента. Типовые логические элементы и их обозначения на функциональных схемах.

Определение: как правило ,под логическим элементом понимается комбинационная схема ,реализующая некоторую элементарную булеву функцию.

Любой логический элемент характеризуется :

Наличием одного или нескольких входов на которые подаются входные сигналы( входные переменные).

Наличием выхода ,на котором формируется выходной сигнал

(выходная переменная).

Определенной функцией ,которая отображает зависимость выходного сигнала от входных.

К основным типам логических элементов относятся:

Инвертор( НЕ)

Дизъюнктор (ИЛИ)

Конъюнктор (И)

Дизъюнктор с отрицанием (ИЛИ - НЕ)

Конъюнктор с отрицанием (И - НЕ)

Исключительное ИЛИ

(единичный сигнал на выходе имеет место в том и только том случае если на

одном и только одном входе присутствует единичный сигнал)

Сумматор по модулю 2

1)Элементы 1,2,3 образуют булев базис.

2)Элементы 1 и 2 или 1 и 3 образует сокращенный(неполный)

булев базис.

3)Элементы 4 или 5 образуют универсальный базис.

4)Элементы 3 и 7 образуют базис Жегалкина.

Функции элементов 6 и 7 совпадают при наличии только двух входов.

Понятие двоичного сигнала. Способы его кодирования.

В связи с использованием двух значений логики в логических схемах как входные ,так и выходные сигналы в этих схемах представляются с помощью так называемого двоичного сигнала - особенностью которого является наличие двух четко различимых уровней ,отождествляемых с нулем и единицей.

В зависимости от того ,какой уровень сигнала сопоставляется с логическим нулем а какой с логической единицей различают два способа кодирования двоичных сигналов:

1)Позитивное кодирование (положительное)

высший уровень сигнала - 1 ,низший - 0

2)Негативное кодирование (отрицательное)

высший уровень сигнала - 0 ,низший - 1

При изменении способа кодирования двоичного сигнала функция одной и той же электронной схемы ,реализующей некоторый логический элемент меняется на противоположную.

Понятие логической системы. Типы логических систем.

Логическая схема представляет собой совокупность логических элементов и связей между ними.

Соединения логических элементов в рамках единой логической системы должны удовлетворять следующим правилам:

1)К любому входу логического элемента могут быть подключены:

a) выход любого другого логического элемента( в частном случае ,того же самого)

б) входной сигнал (входная переменная)

в) логическая константа(0 или 1)

В реальных электронных схемах подача логической константы на вход элемента реализуется либо заземлением либо подключением этого входа обязательно через резистор к шине питания.

2)Выход любого логического элемента схемы может быть подключен к входу другого логического элемента или представлять собой выходной сигнал схемы .В частном случае возможна комбинация того и другого.

Логические схемы разделяются на два типа :

1)Комбинационные

2)Последовательносные

В комбинационных схемах значение выходного сигнала в любой момент времени зависит только от комбинации входных сигналов (в этот же момент времени с учетом задержки распространения сигнала по элементам схемы)

С учетом этой задержки значение выходного сигнала по времени запаздывает на время задержки по сравнению с моментом изменения входных сигналов.

Функционирование комбинационной схемы может быть описано булевой функцией, отражающей зависимость выходного сигнала схемы, как функции от входных сигналов , как аргумент этой функции.

Для комбинационных схем с несколькими выходами эта зависимость отражается системой булевых функций.

Пример комбинационной схемы на элементах булева базиса :

В последовательносных схемах выходные сигналы в любой момент времени зависят не только от комбинации входных сигналов в данный момент времени ,но и от предыстории их изменения ,то есть от последовательности входных сигналов во времени. Как правило последовательносные схемы характеризуются некоторым внутренним строением ,от которого зависит значение выходного сигнала(ов).

Внутреннее состояние такой схемы сохраняется на запоминающих элементах (триггерах) ,в связи с чем ,схемы этого типа называются схемами с памятью.

В общем случае поседовательносная схема представляет собой некоторый цифровой автомат.

Пример последовательносной схемы: (универсальный базис И-НЕ)

Последовательносные схемы характеризуются наличием так называемых петель ,по которым выход некоторого элемента соединяется со входом этого же самого элемента (через другие элементы схемы).

Основные параметры комбинационной схемы.

Основными параметрами комбинационных схем (КС) является стоимость и быстродействие ,как правило при построении абстрактных КС не привязанных к конкретной системе элементов цена схемы определяется в смысле Квайна. Быстродействие схемы ,как правило оценивается задержкой распространения сигналов от входов схемы к ее выходу. Для абстрактных КС эту задержку принято считать в виде : Т=кt ,t-задержка на одном логическом элементе,к-максимальное количество логических элементов ,через которые проходит сигнал от входов к выходу.

Как правило задержка схемы сопоставляется с числом уровней этой схемы. Для этой цели все элементы схемы распределяются по уровням. Уровень элемента ,на выходе которого формируется выходной сигнал схемы совпадает с количеством уровней схема и следовательно с ее задержкой.

Для приведенной схемы элементы 1,2,3 относятся к первому уровню.

Элементы 4,5 ко второму уровню.

Элемент 6 к третьему уровню.

Элемент 7 к четвертому уровню.

studfiles.net

Видеоматериалы

Опыт пилотных регионов, где соцнормы на электроэнергию уже введены, показывает: граждане платить стали меньше

Подробнее...С начала года из ветхого и аварийного жилья в республике были переселены десятки семей

Подробнее...Более 10-ти миллионов рублей направлено на капитальный ремонт многоквартирных домов в Лескенском районе

Подробнее...Актуальные темы

ОТЧЕТ о деятельности министерства энергетики, ЖКХ и тарифной политики Кабардино-Балкарской Республики в сфере государственного регулирования и контроля цен и тарифов в 2012 году и об основных задачах на 2013 год

Подробнее...Предложения организаций, осуществляющих регулируемую деятельность о размере подлежащих государственному регулированию цен (тарифов) на 2013 год

Подробнее...

КОНТАКТЫ

360051, КБР, г. Нальчик

ул. Горького, 4

тел: 8 (8662) 40-93-82

факс: 8 (8662) 47-31-81

e-mail:

Этот адрес электронной почты защищен от спам-ботов. У вас должен быть включен JavaScript для просмотра.