Справочник «Цифровые Интегральные Микросхемы»

Справочник «Цифровые Интегральные Микросхемы»

[ Содержание ]

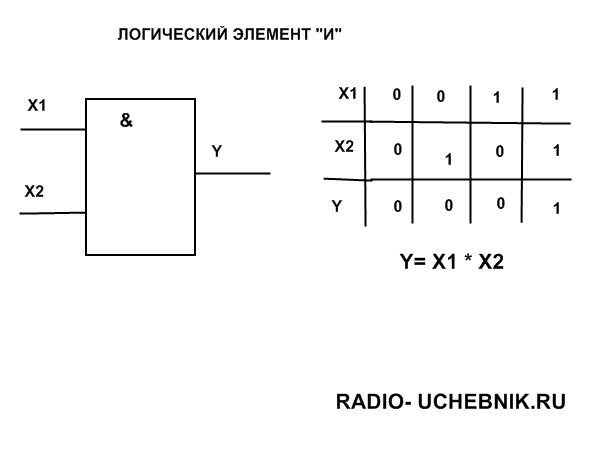

2.4.2 Микросхемы типа ЛА, ЛИ

Чтобы рассмотреть схемотехнику, составим таблицу функций элементов И,

И-НЕ для двух входов А и В (простейший вариант). Каждая переменная

А и В моделируется электронным ключом, который можно замкнуть или разомкнуть.

Если ключи соединены последовательно, то они работают согласно логике И: ток

в цепи появится, если замкнуть оба ключа: и А и В. Если активными входными

сигналами считать замыкание ключей А и В и назвать это событие логической 1,

то, последовательно перебирая состояние этих ключей, составим таблицу входных

и выходных данных для элементов И и И-НЕ.

| Логический элемент | Входные переменные | Выходная функция | ||

|---|---|---|---|---|

| А | B | И | НЕ-И | |

| 0 | 0 | 0 | 1 | |

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

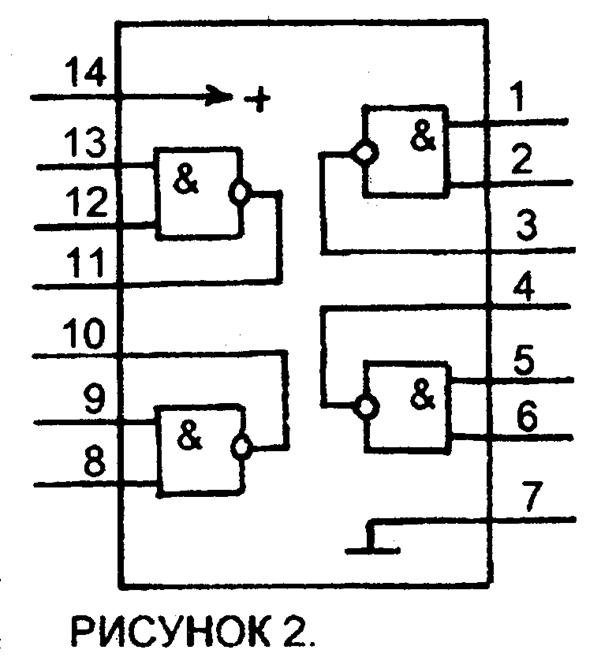

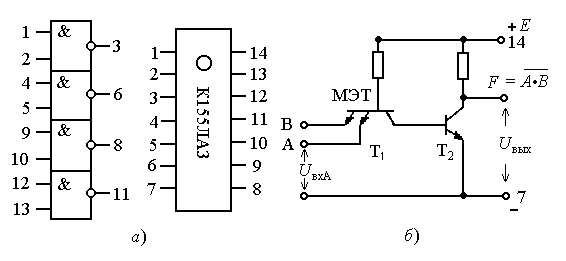

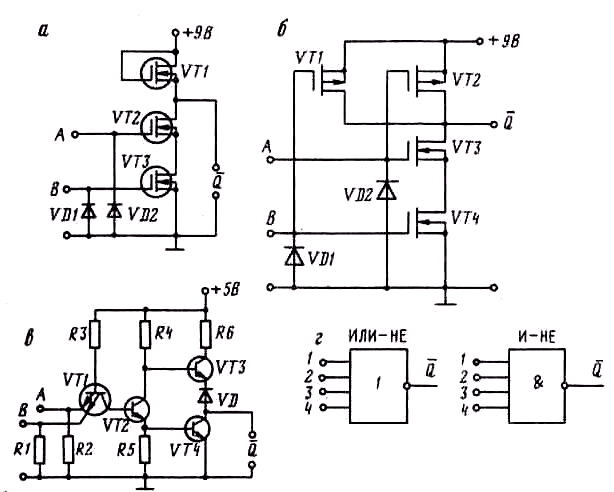

Рассмотрим способ реализации логической операции И-НЕ на элементах ТТЛ. На рис. 2.8, а приведена

На рис. 2.8, а приведена

принципиальная схема двухвходового логического элемента И-НЕ.

Рис. 2.8.а. Принципиальная схема логического элемента.

Подавая от ключей S1 и S2 на входы А и В напряжение высокого В и низкого Н уровней,

составим таблицу выходных уровней элемента.

| Вход | Выход Q(НЕ-И) | Вход | Выход Q(НЕ-И) | ||

|---|---|---|---|---|---|

| А | B | A | B | ||

| Н | Н | В | 0 | 0 | 1 |

| Н | В | В | 0 | 1 | 1 |

| В | Н | В | 1 | 0 | 1 |

| В | В | Н | 1 | 1 | 0 |

Напряжение низкого уровня Н появляется на выходе Q, когда

на обоих входах А и В присутствует высокое напряжение В.

Условное графическое обозначение двухвходового логического

элемента показано на рис 2.8, в

Рис 2.8.в. Условное обозначение элемента.

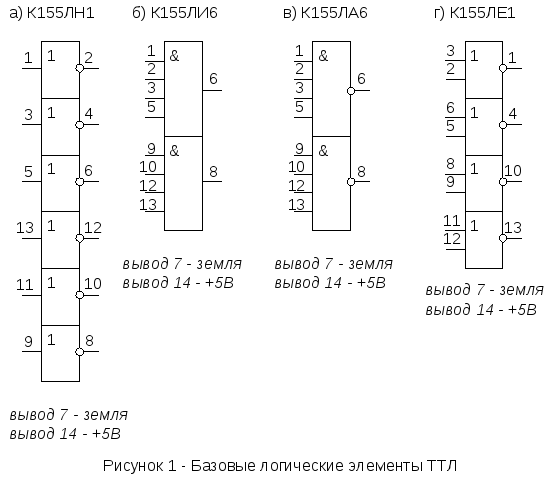

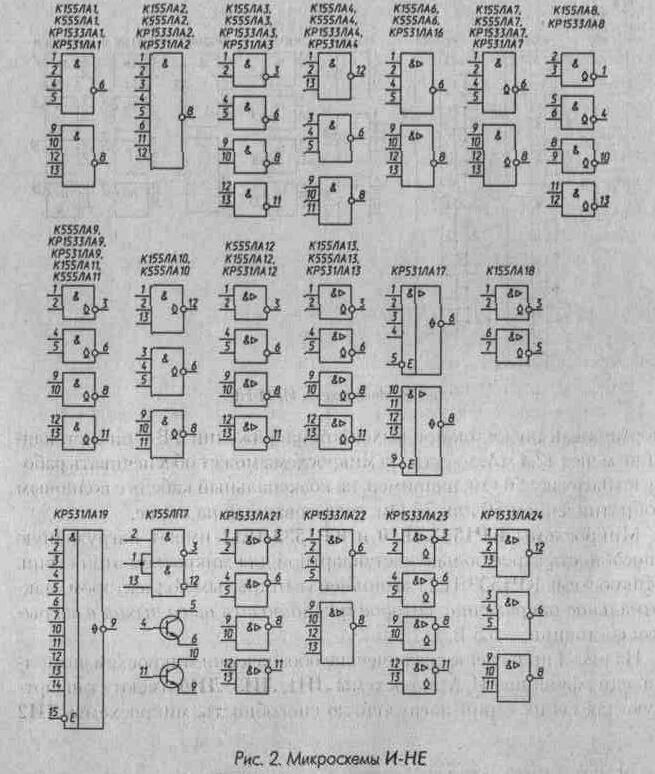

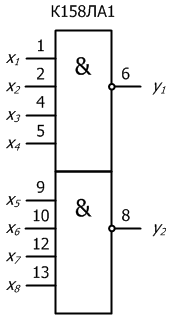

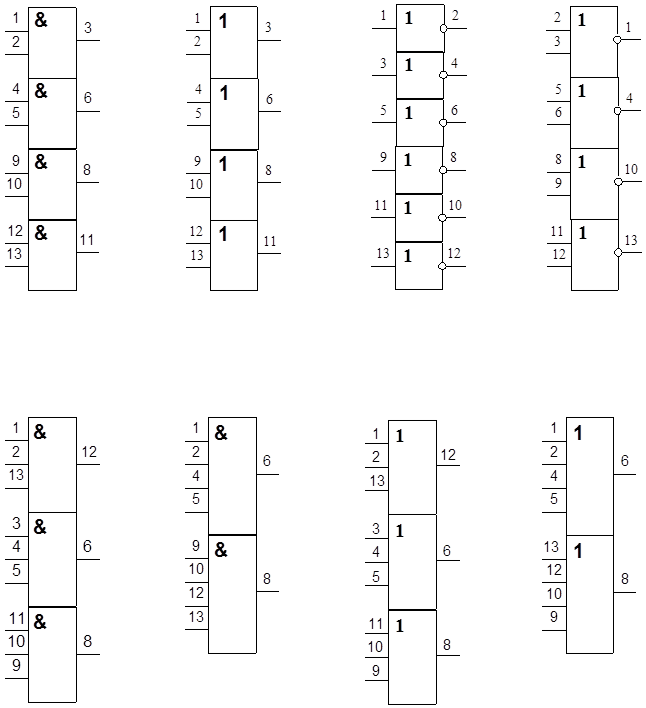

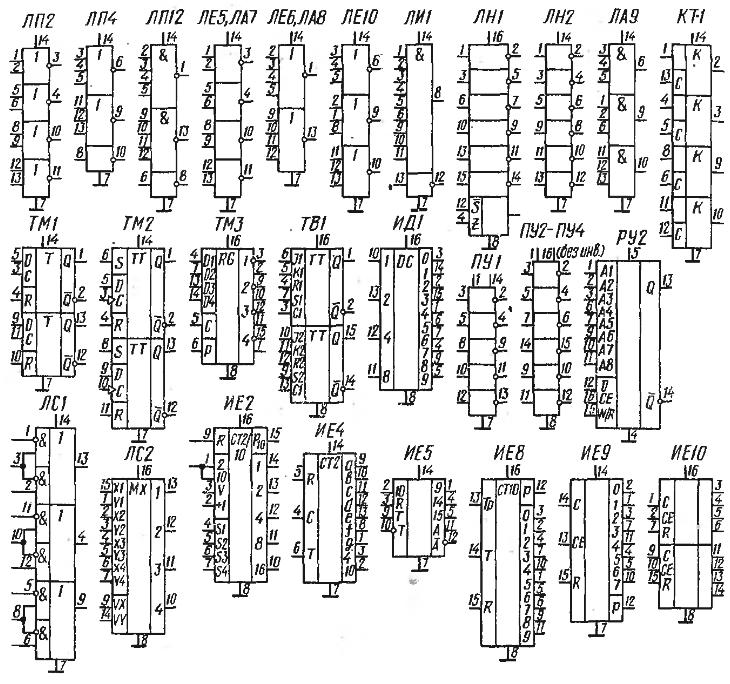

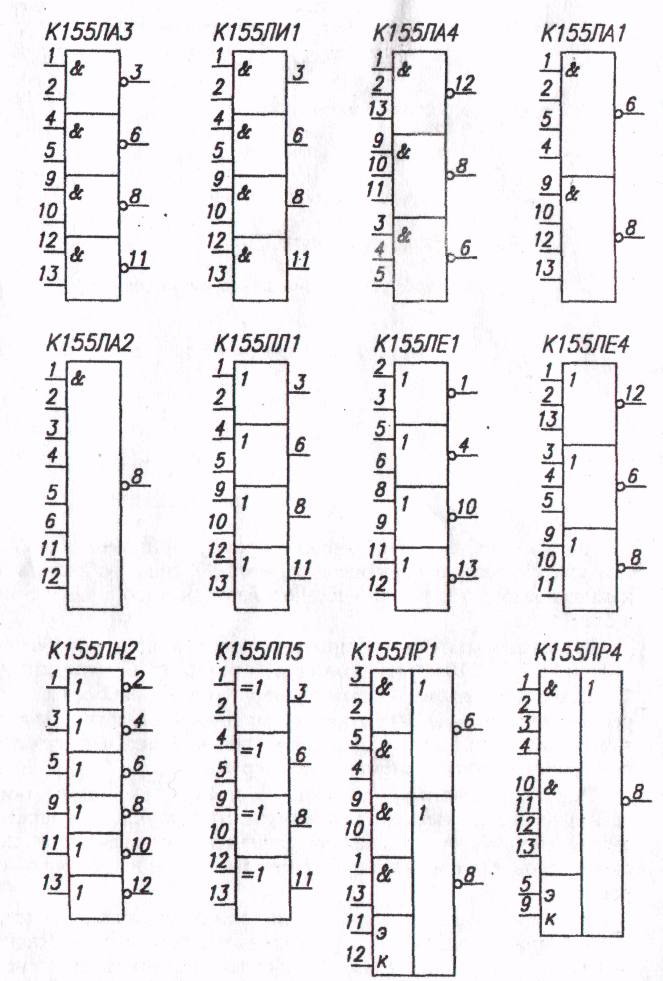

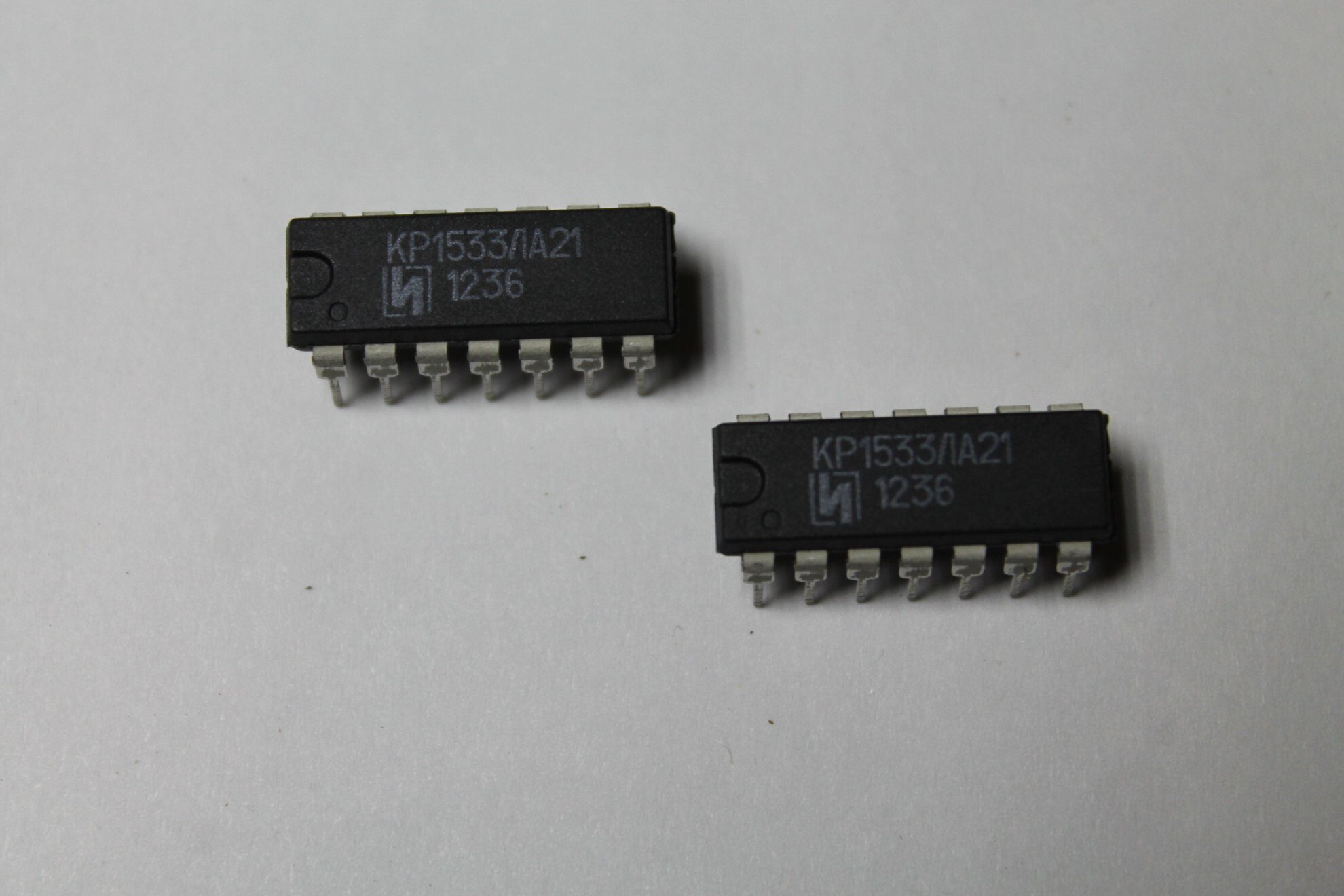

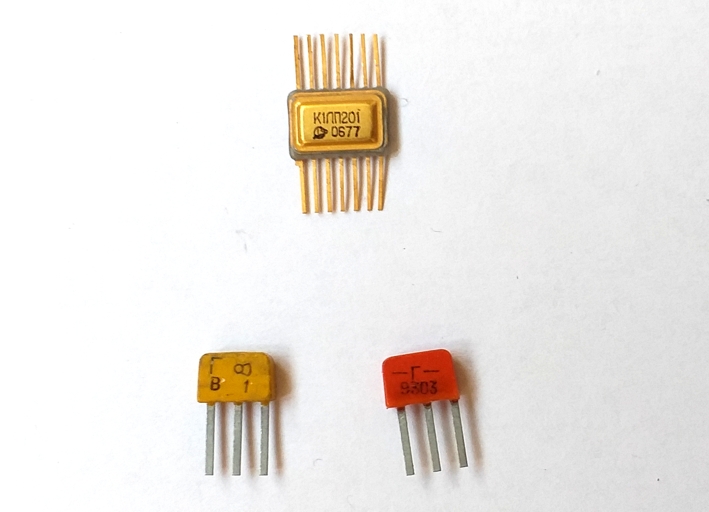

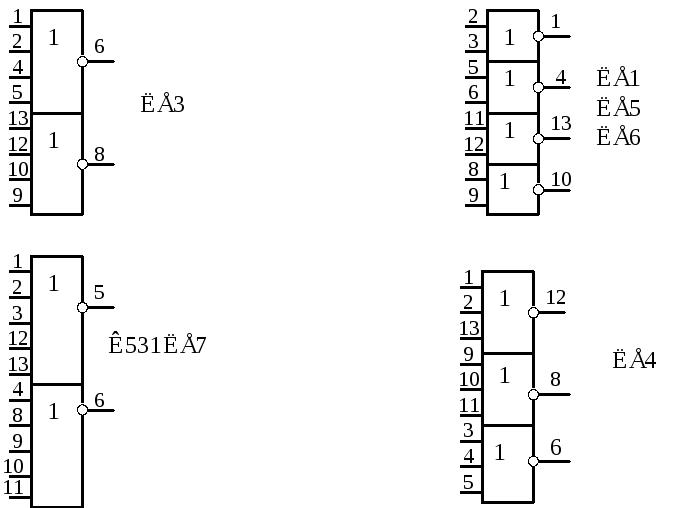

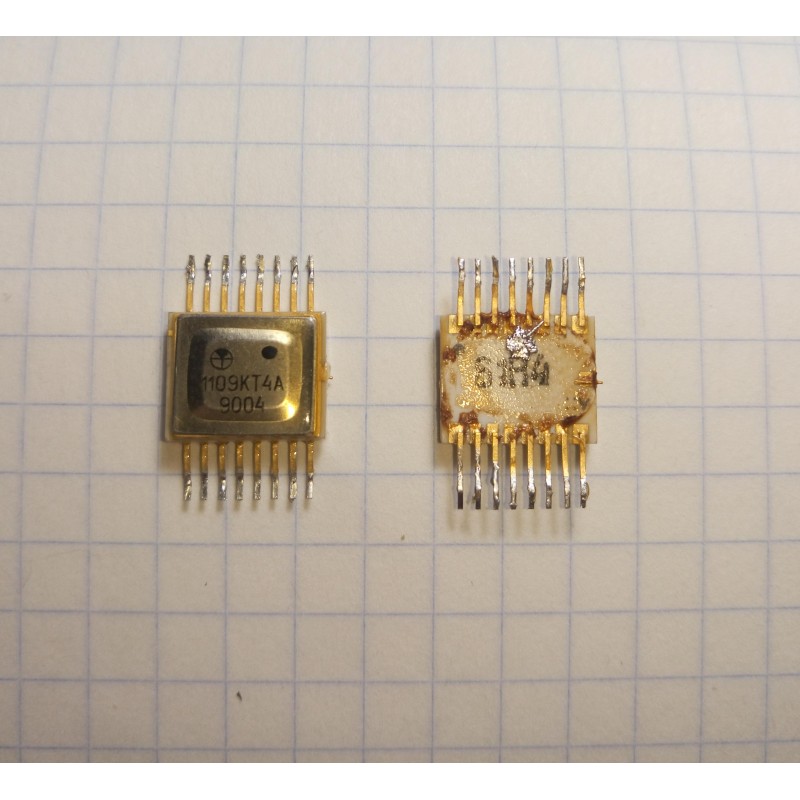

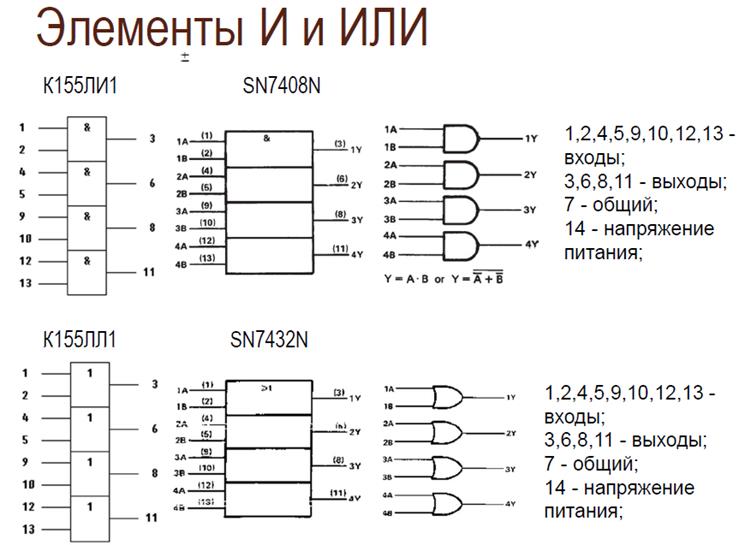

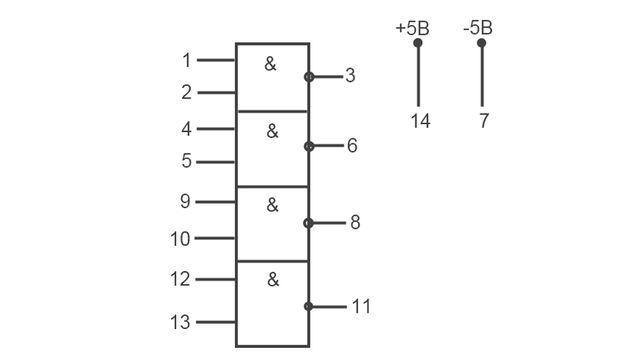

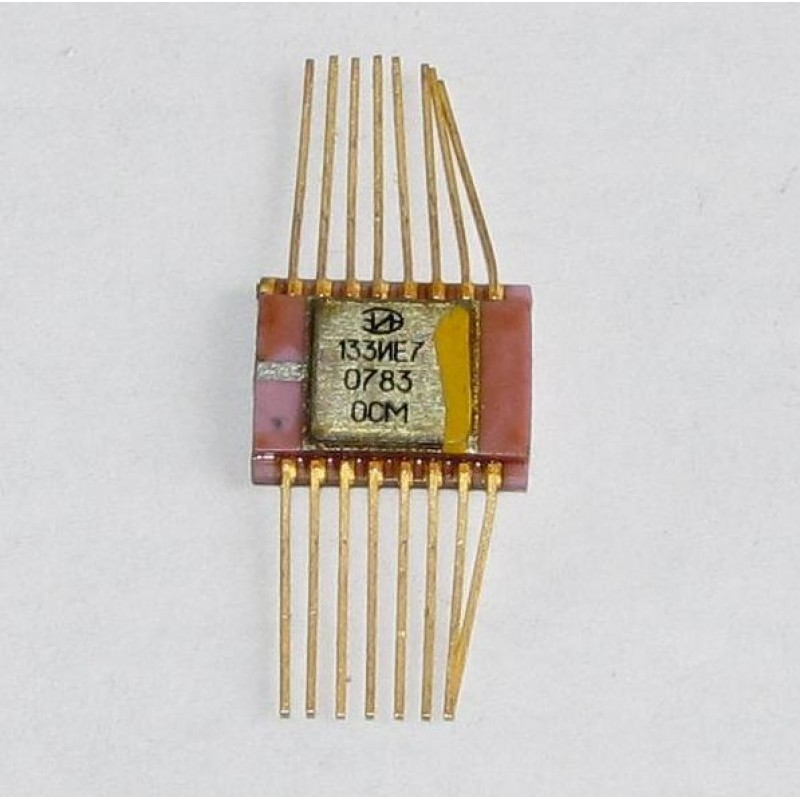

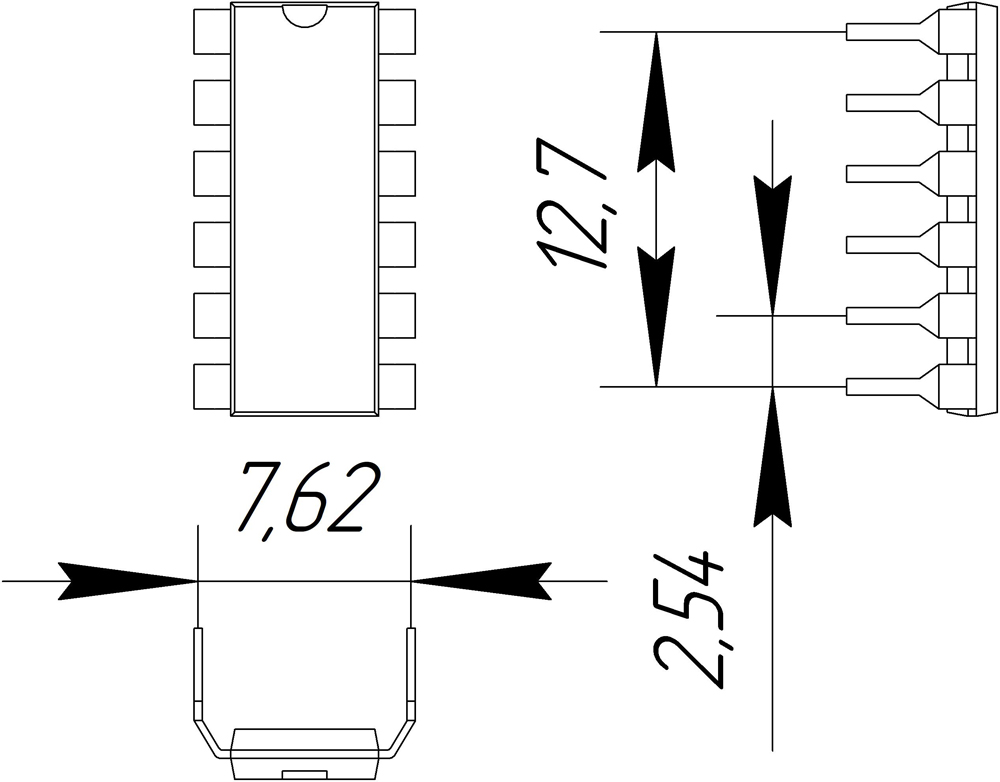

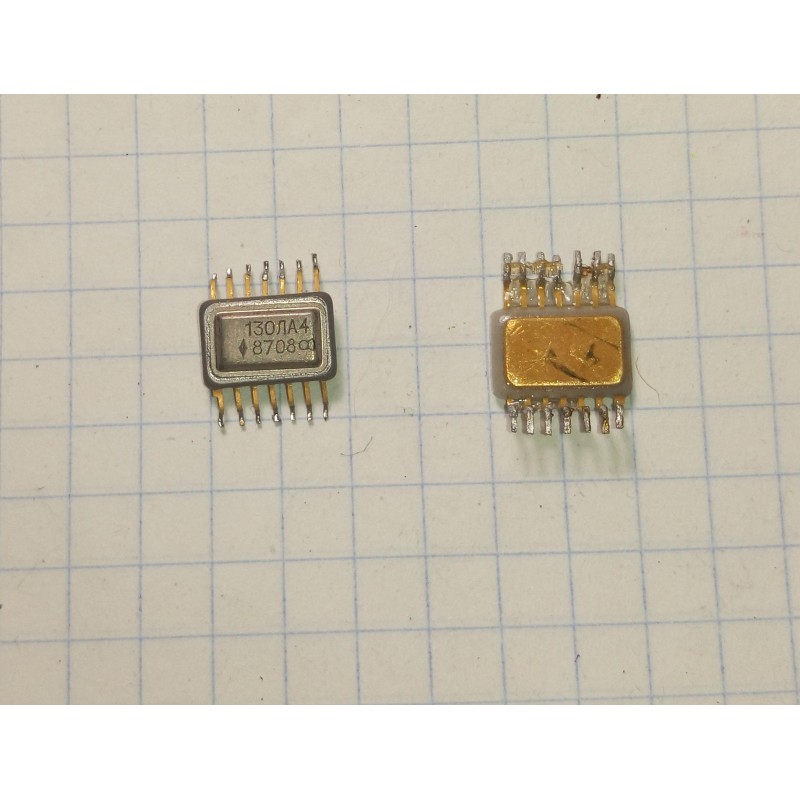

Среди простейших ИС ТТЛ преобладают элементы И, И-НЕ.

Каждый из корпусов ИС типа ЛА и ЛИ содержит от двух до

четырех логических элементов, а микросхемы ЛА2 и ЛА19

содержат по одному логическому элементу И-НЕ на восемь

и двенадцать входов соответственно.

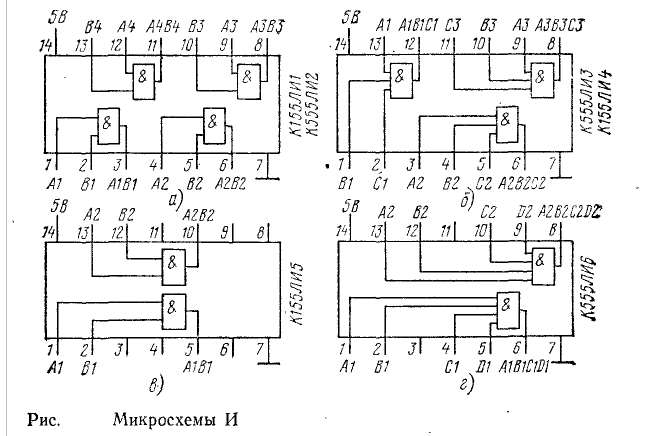

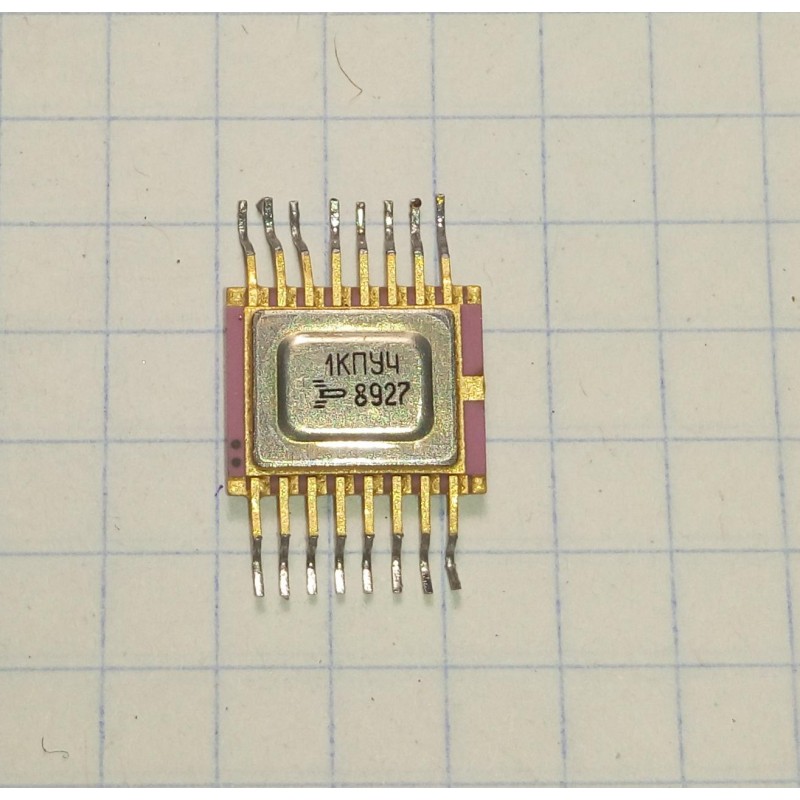

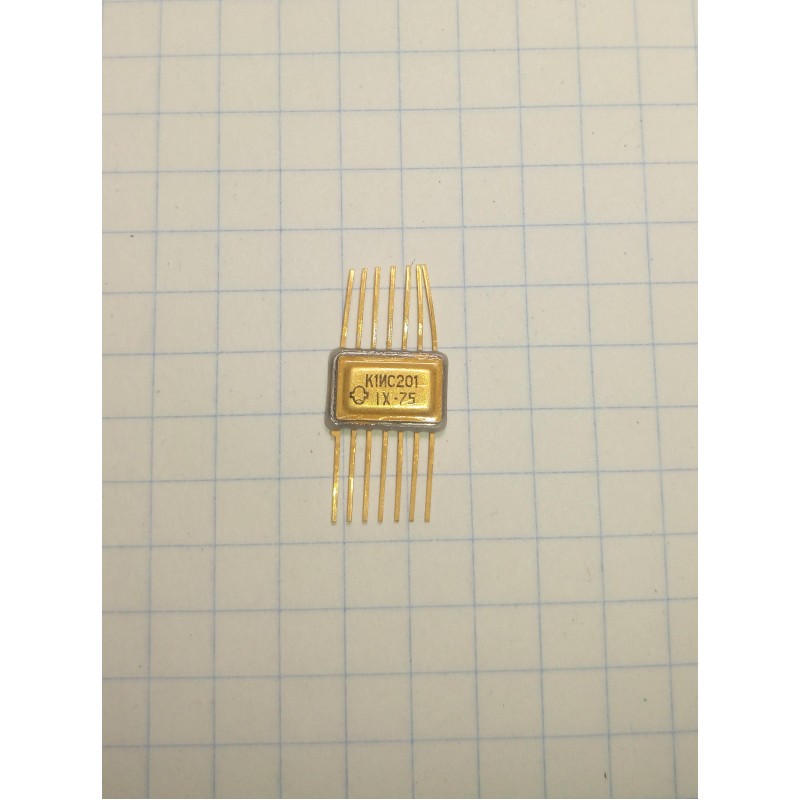

Цоколевки микросхем типа ЛА и ЛИ и их условные графические

обозначения приведены на рис. 2.9, а основные параметры даны

в табл. 2.3.

Рис 2.9. Условные обозначения и цоколевки микросхем ЛИ

Рис 2.9. Условные обозначения и цоколевки микросхем ЛА

Следует особо выделить группу микросхем, логические элементы

которых имеют выходы с открытым коллектором (ЛА7…ЛА11, ЛА13. ЛА18),

(ЛИ2, ЛИ4, ЛИ5). Схема двухвходового логического элемента И-НЕ с

открытым коллектором показана на рис. 2.10, а.

Рис. 2.10а. Принципиальная схема логического элемента И-НЕ

Для формирования выходного перепада напряжения к выходу такого

элемента необходимо подключить внешний нагрузочный резистор Rн.

Такие микросхемы применяются для обслуживания сегментов индикаторов,

зажигания ламп накаливания, светодиодов (рис. 2.10,б).

Рис. 2.10б. Схема подключения ламп накаливания и светодиодов

При необходимости в схемах можно использовать элемент ТТЛ

с двухтактным выходом. Для некоторых микросхем с открытым

коллекторным выходом (ЛА11) нагрузку можно подключать к более

высоковольтному источнику питания (рис. 2.10,в).

Рис. 2.10в. Схема подключения нагрузки к высоковольтному источнику

Такое включение необходимо для зажигания газоразрядных и

электролюминесцентных индикаторов. Выходы с открытого коллектора

используют для подключения обмоток реле.

Выходы нескольких элементов с открытым коллектором

можно присоединять к общей нагрузке Rн (рис. 2.10, г).

Рис. 2.10г. Схема подключения нескольких элементов к общей нагрузке

Такое подключение позволяет реализовать логическую функцию И,

называемую «монтажное И». Схему (рис. 2.10. г) используют

для расширения числа входов логического элемента.

Следует помнить, что двухтактные выходы ТТЛ нельзя

соединять параллельно, это приводит к токовой перегрузке

одного из элементов.

Многовходовые составные логические элементы с открытым

коллектором и общим сопротивлением нагрузки Rн реализуются

наиболее просто, однако они не позволяют получить

предельное быстродействие. Более лучший способ

увеличения числа входов осуществляется с помощью

специальной микросхемы-расширителя, имеющей

дополнительные выводы коллектора и эмиттера

фазоразделительного каскада VT2 (рис. 2.11).

Одноименные вспомогательные выводы нескольких таких

элементов можно объединять.

Рис. 2.11а. Принципиальная схема 2И-НЕ с дополнительными выводами коллектора и эмиттера.

Рис. 2.11б. Условное обозначение расширителя и способ соединения нескольких микросхем.

Микросхема К531ЛА16 (магистральный усилитель) может

передавать данные в линию с сопротивлением 50 Ом.

Микросхемы ЛА17, ЛА19 — это логические элементы И-НЕ с

тремя состояниями на выходе, т. е. они имеют дополнительный

е. они имеют дополнительный

вход /ЕО (Enable output), дающий разрешение по выходу.

На рис. 2.12 показана схема элемента, который имеет третье

выходное состояние Z, когда выход размыкается.

Рис. 2.12. Принципиальная схема логического элемента с тремя состояниями на выходе.

Для этой цели в схему стандартного сложного инвертора ТТЛ вводится

дополнительный инвертор DDI и диод VD2. Если на этот вход /ЕО подать

от переключателя S1 напряжение высокого уровня — 1, то выходное

напряжение инвертора DD1 станет низким, т. е. катод диода VD2 будет

практически соединен с корпусом. Из-за этого коллектор транзистора

VT2 будет иметь нулевой потенциал, т. е. транзистор VT2 будет закрыт.

Транзисторы VT3 и VT4 будут находиться в режиме отсечки, т. е.

оба закрыты. Следовательно, выходной вывод как бы «висит» в воздухе,

микросхема переходит в состояние Z с очень большим выходным сопротивлением.

Если на вход ЕО подается разрешающий низкий уровень — О, то логический

элемент И-НЕ работает как в обычном режиме.

| Вход | Выход | ||

|---|---|---|---|

| /EO | I | /Y | |

| 0 | 0 1 | 1 0 | |

| 1 | 0 1 | Z | |

Такие логические элементы разработаны специально для

обслуживания проводника шины данных. Если к такому

проводнику присоединить много выходов, находящихся в

состоянии Z, то они не будут влиять друг на друга.

Активным передающим сигналом должен быть лишь один

логический элемент, только от его выхода в проводник

шины данных будет поступать информация. Следовательно,

соединенные вместе выходы не должны быть одновременно активными.

Чтобы сигналом разрешения (низкий уревень — О) , подаваемым

на вход /EO, подключался к проводнику выход только одного

логического элемента, необходимо предусмотреть дополнительный

(защитный) временной интервал, т. е. переключать входы /ЕО

е. переключать входы /ЕО

различных элементов с паузой. Сигналы разрешения, даваемые

выходам разных элементов, не должны

перекрываться.

Микросхема К531ЛА19-это 12-входовый логический элемент И-НЕ с

дополнительным инверсным входом /ЕО. Сигнал появится на его

выходе, если на вход /ЕО подано напряжение низкого уровня — О.

Выход логического элемента перейдет в разомкнутое состояние Z,

если на вход /ЕО подается напряжение высокого уровня. В состоянии

Z элемент потребляет ток Iпот.z=25 мА. Время задержки перехода

выхода к разомкнутому состоянию tзд.1z= 16 нс, время задержки

перехода выхода tзд.0z= 12 нс (от напряжения низкого выходного

уровня), при условии, что Сн = 15 пФ [1].

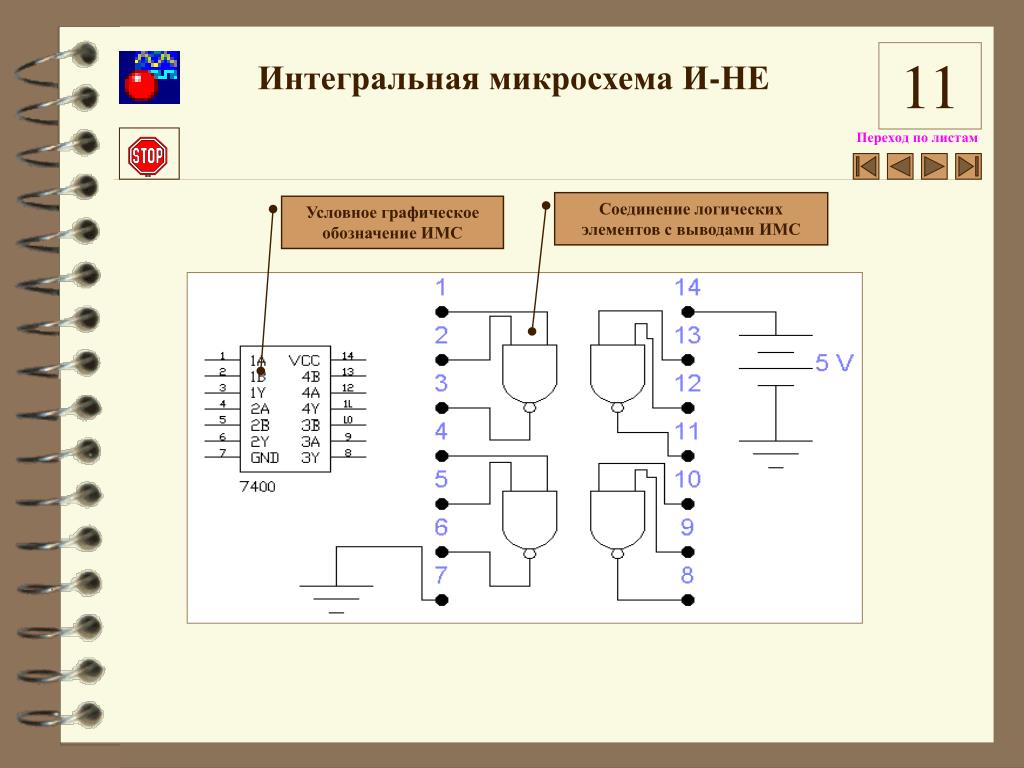

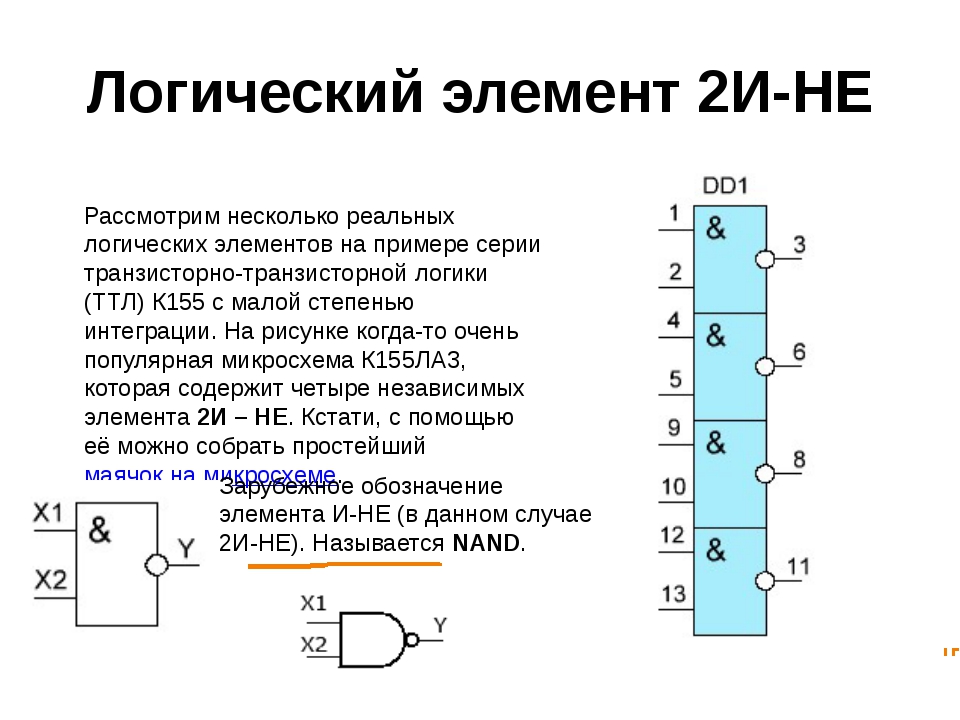

Логический элемент 2И-НЕ и его характеристики

1.2. Логический элемент 2И-НЕ и его характеристики

Широкое распространение получили

логические элементы транзисторно-транзисторной логики (ТТЛ). Рассмотрим

принципиальную схему логического элемента 2И-НЕ

транзисторно-транзисторной логики со сложным инвертором на выходе. Такие логические

Такие логические

элементы имеют хорошую нагрузочную способность.

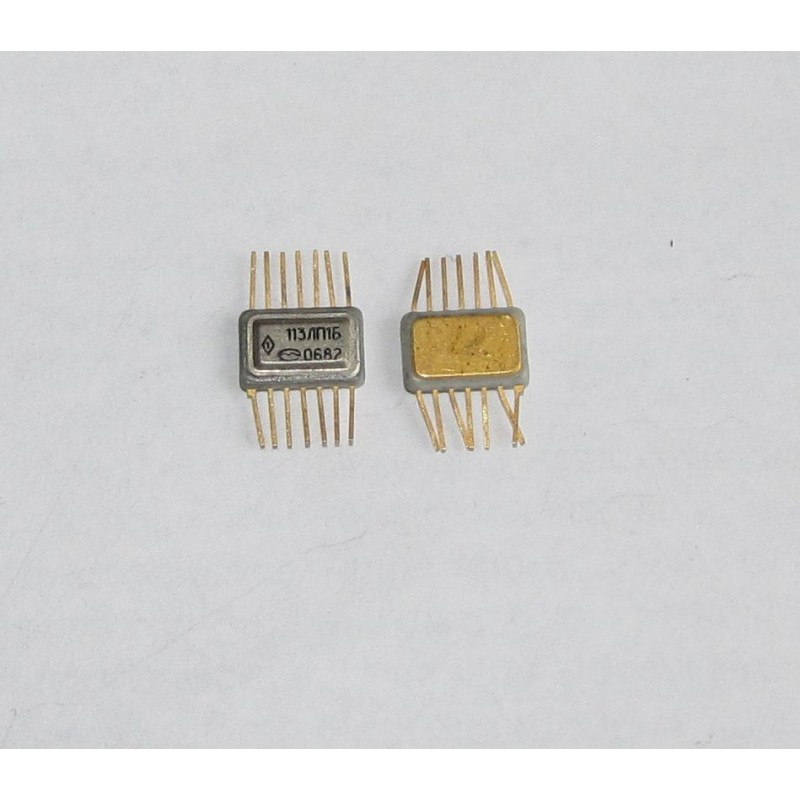

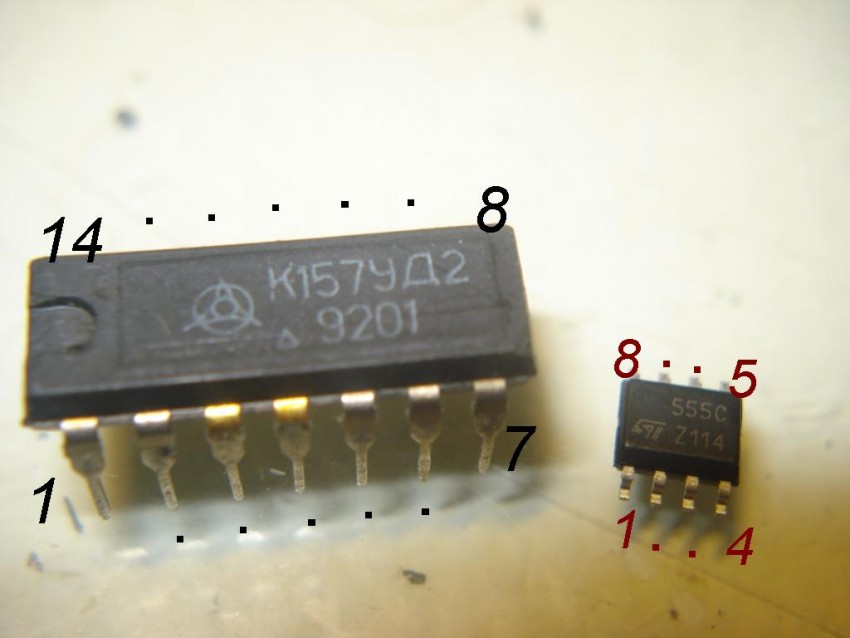

На рисунке 1.14,а приведена принципиальная

схема одного из четырех логических элементов 2И-НЕ микросхемы К134ЛБ1, а на

рисунке 1.14,б – условное обозначение этой микросхемы на принципиальных

схемах.

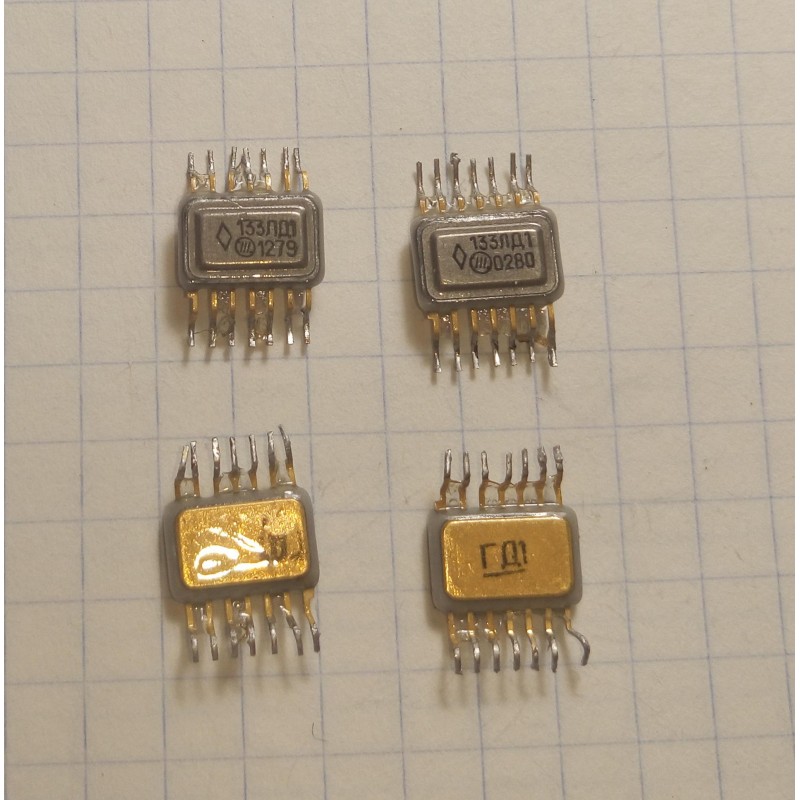

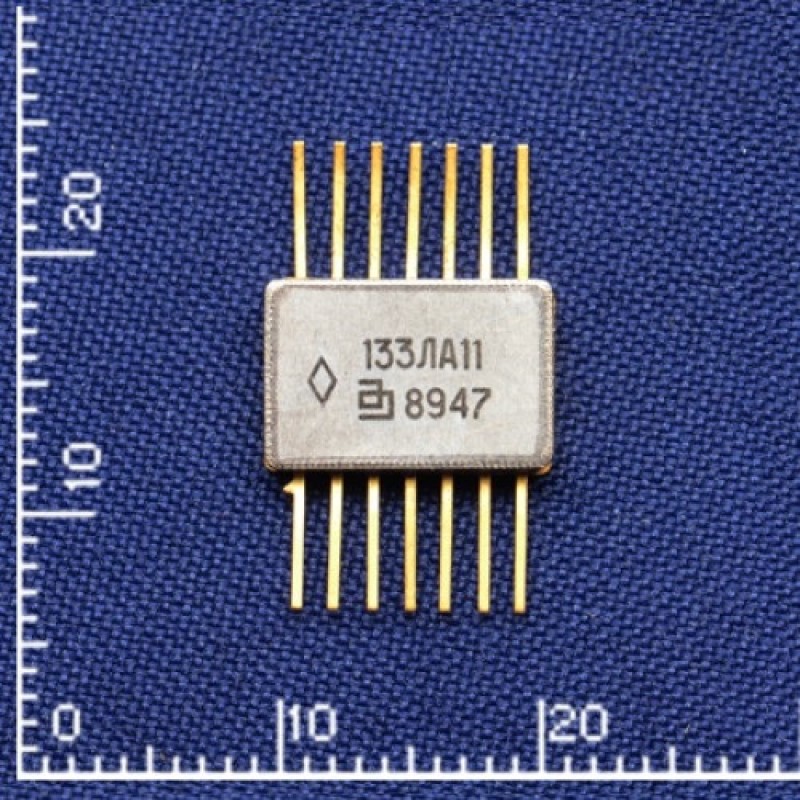

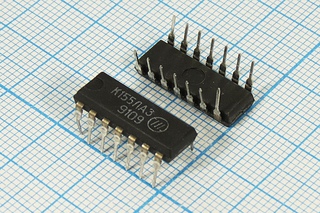

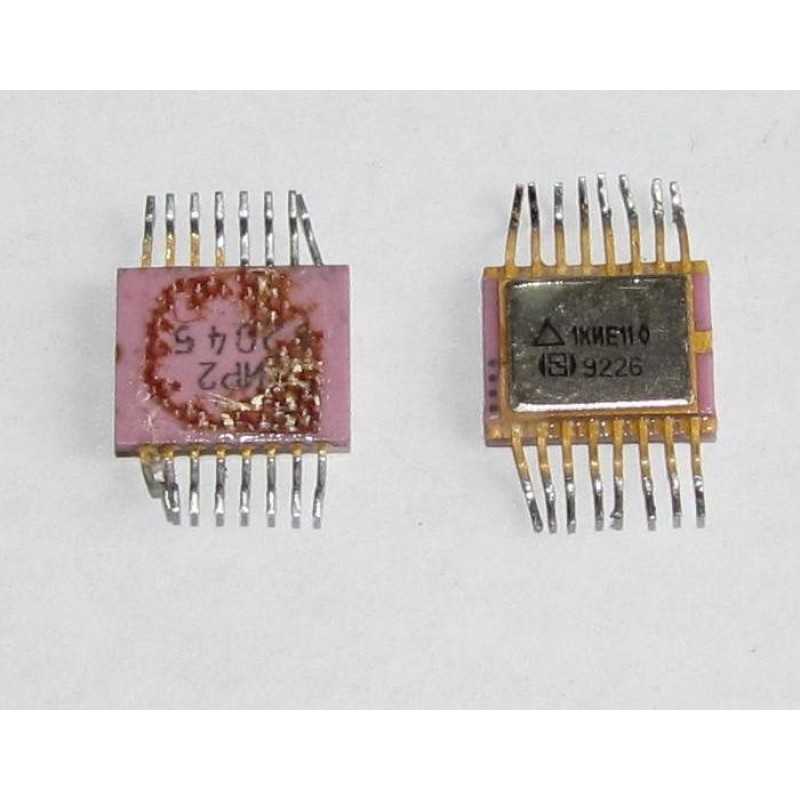

На рисунках 1.15,а и 1.15,в приведены принципиальные

схемы логических элементов 2И-НЕ соответственно для микросхем К133ЛА3 и

К155ЛА3. Каждая их этих микросхем имеет по 4 логических элемента 2И-НЕ, а их

условные обозначения на принципиальных схемах совпадают (рис. 1.15,б).

Первые логические

элементы ТТЛ не имели на входах защитных диодов. В момент окончания

прямоугольного импульса на входе элемента в монтажных цепях цифрового

устройства могут возникнуть затухающие колебания. Следствием этих колебаний

может быть ложное срабатывание цифрового устройства. В результате доработки логических

элементов к каждому входу многоэмиттерного

транзистора были подключены демпфирующие диоды. Первым отрицательным

Первым отрицательным

импульсом затухающего колебания демпфирующий диод открывается, и амплитуда

затухающих колебаний резко уменьшается. Следующий положительный импульс

затухающего колебания уже не может изменить состояние на выходе логического

элемента.

Резисторы R4, R5 и

транзистор VT5 в

логическом элементе 2И-НЕ микросхемы К155ЛА3 (рис. 1.15,в) позволяют получить

передаточную характеристику, более близкую к прямоугольной. Это повышает

помехозащищенность в состоянии логической единицы на выходе элемента.

Рассмотрим работу логического элемента 2И-НЕ

микросхемы К134ЛБ1 (рис. 1.14,а). Для логических элементов

транзисторно-транзисторной логики напряжение логического нуля по техническим

условиям может быть 0-0,4 В. Напряжение логической единицы — не менее 2,4 В и

не более 5 В. Напряжение логического нуля можно подать, соединив вход элемента

с общим проводом накоротко, либо через резистор малого сопротивления (не более

300 Ом). Напряжение логической единицы на вход элемента можно подать, соединив

вход элемента с плюсовым проводом питания через резистор сопротивлением 1 Ком, либо оставляя вход элемента

свободным.

Пусть на входы

Х1 и Х2 элемента 2И-НЕ (рис. 1.14,а)

поданы напряжения логической единицы. Рассмотрим случай, когда Х1 и Х2 никуда не подключены. В этом случае

транзисторы VТ2, VТ4 будут

открыты токами базы, протекающими по цепи: + источника, резистор R1, переход база-коллектор VТ1,

база-эмиттер VТ2,

база-эмиттер VТ4, минус

источника. Транзистор VТ3

в этом случае закрыт, т.к. потенциал коллектора

транзистора VT2

примерно 0,9 В.

Рассмотрим

делитель напряжения, верхнее плечо которого состоит из последовательно

соединенных резистора R3,

выводов коллектор-эмиттер транзистора VТ3, диода VД1,

а нижнее плечо делителя – это выводы коллектор-эмиттер VТ4. В рассматриваемом случае

сопротивление верхней части делителя велико, а сопротивление нижней части

делителя — мало. Выходное напряжение соответствует логическому нулю.

Если хотя бы на

одном из входов Х1, Х2 действует логический нуль, то VТ2, VТ4 закрыты, а VТ3 открыт. Ток базы транзистора VT3 протекает по цепи: плюс источника

питания, резистор R2,

переход база-эмиттер транзистора VT3, полупроводниковый диод VD1, резистор нагрузки (на схеме не показан), минус источника

питания. В этом случае сопротивление

В этом случае сопротивление

между коллектором транзистора VT3 и катодом диода VD1 мало, а сопротивление между коллектором и эмиттером

транзистора VT4 велико.

Анализируя делитель напряжения, приходим к выводу, что выходное напряжение

логического элемента будет соответствовать логической единице.

В

вычислительной технике широко применяется устройство с тремя состояниями на

выходе. Рассмотрим логический элемент НЕ (инвертор) с тремя состояниями на выходе (рис. 1.16,а). Указанный инвертор

легко получается из схемы базового логического элемента 2И-НЕ путем добавления

в схему VД2.

Если на вход

разрешения V микросхемы подано напряжение

логической «1», то диод VД2

оказывается отключенным от схемы, и данный элемент можно рассматривать как

логический элемент НЕ. Если на

входе Х логическая единица, то транзисторы VT2, VT4 будут

открыты, транзистор VT3 закрыт и на выходе элемента

будет сигнал логического нуля. Подадим на вход Х сигнал логического нуля. В

В

этом случае транзисторы VT2, VT4 будут закрыты, транзистор VT3 открыт и на выходе элемента будет сигнал логической

единицы.

Подадим на вход V

напряжение логического «0» , в этом случае

окажутся закрытыми VТ2, VТ3, VТ4. Выход Y

оказывается отключенным как от плюсового,

так и от минусового проводов источника питания. Говорят, что выход

элемента находится в третьем высокоимпедансном состоянии (состояние высокого

сопротивления, как от клеммы «+», так и от клеммы «-» источника питания). Элементы с тремя

состояниями позволяют организовать в компьютерных системах так называемую общую

шину.

Элементы с тремя состояниями входят в состав шинных формирователей. Шинные формирователи это устройства, которые обеспечивают передачу

сигнала в двух направлениях по

одному и тому же проводу. В составе шинного формирователя на каждую линию

потребуется 2 элемента с тремя состояниями на выходе.

На рисунке

1.16,б приведена схема логического элемента 2И-НЕ с открытым коллектором на

выходе. Выходы нескольких таких элементов подключаются к одному резистору

Выходы нескольких таких элементов подключаются к одному резистору

нагрузки, второй вывод которого подключен к плюсовому проводу источника питания.

На рисунке

1.17,а приведена схема подключения приборов для снятия зависимости выходного

напряжения логического элемента от тока нагрузки в состоянии логической единицы

на выходе элемента, а на рисунке 1.18,а – график этой зависимости. Логические

элементы ТТЛ не выходят из строя при коротком замыкании нагрузки для случая

логической единицы на выходе элемента, поэтому в цепи нагрузки нет

необходимости ставить ограничительный резистор. Если на выходе элемента

логический нуль, то при исследовании

зависимости выходного напряжения от тока нагрузки необходимо в цепи

нагрузки устанавливать ограничительный резистор.

На рисунке

1.17,б приведена схема подключения приборов для снятия зависимости выходного

напряжения логического элемента от тока нагрузки в состоянии логического нуля на выходе элемента, а на рисунке

1. 18,б – график этой зависимости. Сопротивление ограничительного

18,б – график этой зависимости. Сопротивление ограничительного

резистора в цепи нагрузки выбирают примерно таким же, как сопротивление резистора R3 в логическом элементе 2И-НЕ (рисунок 1.15,в),

т.е. примерно 100 Ом.

По графикам,

приведенным на рисунке 1.18 можно определить коэффициент разветвления или

нагрузочную способность логического элемента. По графику рисунка 1.18,а найдем

ток нагрузки при выходном напряжении 2,4 В. Зная, что входной ток логической

единицы 40 мкА, определим, сколько таких элементов можно подключить в состоянии

логической единицы на выходе данного элемента. По рисунку 1.18,б определим ток

нагрузки в состоянии логического нуля на выходе элемента при напряжении 0,4 В. Зная, что входной ток логического нуля минус 1,6

мА, определим, сколько таких элементов можно подключить в состоянии логического

нуля на выходе данного элемента. Наименьшее из двух полученных значений будет

являться коэффициентом разветвления логического элемента. Определение

коэффициента разветвления таким способом будет справедливо только для низких

частот, когда влиянием входных емкостей элементов и емкости монтажа можно

пренебречь.

На рисунке 1.19,а приведена схема для

наблюдения на экране осциллографа зависимости выходного напряжения элемента от

напряжения на его входе, а на рисунке 1.19,б – график этой зависимости для

логического элемента 2И-НЕ ТТЛ. Диод VD1

может быть любым кремниевым малой мощности, т.к. обратное напряжение в данной

схеме не превысит 5 В, а ток через диод в прямом направлении выбирается единицы

миллиампер. Амплитуда переменного напряжения

на выходе источника переменного напряжения не должна превышать 10 В. График

зависимости выходного

напряжения элемента от напряжения

на его входе называется передаточной характеристикой логического элемента.

Из графика передаточной характеристики логического элемента 2И-НЕ видно, что

при входных напряжениях менее 0,4 В на выходе элемента напряжение логической

единицы, а при входных напряжениях более 2,4 В на выходе элемента напряжение

логического нуля. Реально в логическом элементе входное напряжение логического

нуля может быть больше 0,4 В, а напряжение логической единицы меньше 2,4 В.

Однако, выбирать такой режим работы элемента нецелесообразно, т.к. уменьшается

помехоустойчивость логического элемента.

На рисунке 1.20 приведена входная характеристика логического элемента

2И-НЕ, снятая по одному из входов элемента. На втором входе элемента напряжение

логической единицы. Точка а на

графике входной характеристики соответствует входному напряжению 2,4 В, а точка

б – входному напряжению 0,4 В. Входной ток логической единицы не

превышает 40 мкА, а входной ток логического нуля менее –1,6 мА. Знак минус

означает, что ток вытекает из микросхемы.

На рисунке 1.21,а приведена схема подключения приборов для наблюдения на

экране осциллографа зависимости выходного напряжения от тока нагрузки для

случая, когда на выходе элемента логическая единица. Ограничительный резистор в

цепи нагрузки не предусмотрен, т.к. исследуется логический элемент 2И-НЕ в

состоянии логической единицы на выходе. В качестве источника U2 используется В24, с клемм «+» и «–»

которого снимается пульсирующее с частотой 100 Гц напряжение. Сопротивление

Сопротивление

резистора Rэт выбирают как можно меньше

(коэффициент отклонения по каналу Х осциллографа должен быть минимальным). Если

чувствительность канала Х осциллографа недостаточна, то на вход Х можно

подключить предварительный усилитель. Схема усилителя к входу Х осциллографа

ОМЛ-3М приведена на рисунке 1.22.

Для питания усилителя

используют переменное напряжение 12 вольт. Сопротивление резистора R1 выбирают значительно

больше сопротивления эталонного резистора Rэт. Выход предварительного усилителя подключают к

входу «Х» осциллографа. Переменным резистором R5 проводят балансировку микросхемы DA1 при отсутствии входного

сигнала. Необходимый коэффициент отклонения луча по оси Х устанавливают

переменным резистором R4.

Стабилитроны VD1 и VD2 выбирают с учетом того,

что необходимо обеспечить перемещение луча по оси «Х» из одного крайнего

положения экрана в другое при изменении постоянного напряжения на входе

усилителя от 0 до максимально возможного. Расчет сопротивлений резисторов R6, R7 параметрического

Расчет сопротивлений резисторов R6, R7 параметрического

стабилизатора напряжения проводился с учетом того, что для питания усилителя используется переменное напряжение 12 вольт и выбраны

стабилитроны КС156А.

На рисунке 1.21,б приведена схема подключения приборов для наблюдения на

экране осциллографа зависимости выходного напряжения от тока нагрузки для

случая, когда на выходе элемента логическая нуль. На транзисторах VT1 и VT2 собрано токовое зеркало.

Особенностью работы токового зеркала является то, что коллекторные токи обоих

транзисторов одинаковы и в определенных пределах не зависят от сопротивлений

нагрузок. Значения коллекторных токов определяются напряжением на резисторе R2 и сопротивлениями

резисторов R1 и R3. Сопротивления резисторов R1 и R3 обычно выбирают одинаковыми.

Сопротивление эталонного резистора в данной схеме не обязательно должно быть

малым. Транзисторы VT1,

VT2 должны иметь

примерно одинаковый и достаточно большой коэффициент усиления по току.

В цифровых устройствах на входах логических

элементов обычно присутствуют прямоугольные импульсы напряжения. Пусть

Пусть

напряжение на обоих входах логического элемента 2И-НЕ микросхемы К155ЛА3

скачком изменилось с высокого уровня на низкий (рис. 1.15,в). В этом случае транзистор VT3начнет открываться, а транзистор VT4 – закрываться. Транзисторы открываются

быстрее, чем закрываются. Поэтому в течение некоторого промежутка времени будут

открыты транзисторы VT3 и VT4. Ток, потребляемый

логическим элементом от источника питания, ограничивается только резистором R3. Указанный ток

короткого замыкания приводит к увеличению потребляемой мощности в динамическом

режиме. График зависимости потребляемой от источника питания мощности от

частоты прямоугольных импульсов на входе приведен на рисунке 1.23.

Логический элемент или не кмоп технологии. Характеристики микросхем кмоп и их согласование с логическими элементами других серий

Логические КМОП (КМДП) инверторы

Микросхемы на комплементарных МОП транзисторах (КМОП-микросхемы) строятся на основе МОП транзисторов с n- и

p-каналами. Один и тот же входной потенциал открывает транзистор с n-каналом и закрывает транзистор с p-каналом.

Один и тот же входной потенциал открывает транзистор с n-каналом и закрывает транзистор с p-каналом.

При формировании логической единицы открыт верхний транзистор, а нижний закрыт. В результате ток через КМОП схему

не протекает. При формировании логического нуля открыт нижний транзистор, а верхний закрыт. И в этом случае ток

от источника питания через микросхему не протекает. Простейший логический элемент — это инвертор.

инвертора, выполненного на комплементарных

МОП транзисторах, приведена на рисунке 1.

Рисунок 1. Принципиальная схема инвертора, выполненного на комплементарных МОП транзисторах (КМОП-инвертор)

В результате этой особенности КМОП-микросхем, они обладают преимуществом перед рассмотренными ранее видами

— потребляют ток в зависимости от

поданной на вход тактовой частоты. Примерный график зависимости потребления тока КМОП-микросхемы в зависимости

от частоты ее переключения приведен на рисунке 2

Рисунок 2. Зависимоть тока потребления КМОП микросхемы от частоты

Логические КМОП (КМДП) элементы «И»

Схема логического элемента «И-НЕ»

на КМОП микросхемах практически совпадает с упрощенной

схемой «И» на ключах с электронным управлением, которую мы рассматривали ранее. Отличие заключается в том, что

Отличие заключается в том, что

нагрузка подключается не к общему проводу схемы, а к источнику питания. Принципиальная схема логического элемента

«2И-НЕ » , выполненного на комплементарных МОП транзисторах

(КМОП), приведена на рисунке 3.

Рисунок 3. Принципиальная схема логического элемента «2И-НЕ» , выполненного на комплементарных МОП транзисторах (КМОП)

В этой схеме можно было бы применить в верхнем плече обыкновенный ,

однако при формировании низкого уровня сигнала схема постоянно потребляла бы ток. Вместо этого, в качестве нагрузки

используются p-МОП транзисторы. Эти транзисторы образуют активную нагрузку. Если на выходе требуется сформировать

высокий потенциал, то транзисторы открываются, а если низкий — то закрываются.

В приведённой на рисунке 2 схеме логического КМОП-элемента «И», ток от источника питания на выход

КМОП-микросхемы будет поступать через один из транзисторов, если хотя бы на одном из входов (или на обоих сразу)

будет присутствовать низкий потенциал (уровень логического нуля). Если же на обоих входах логического КМОП-элемента

Если же на обоих входах логического КМОП-элемента

«И» будет присутствовать уровень логической единицы, то оба p-МОП транзистора будут закрыты и на выходе

КМОП микросхемы сформируется низкий потенциал. В этой схеме, так же как и в схеме, приведенной на рисунке 1,

если транзисторы верхнего плеча будут открыты, то транзисторы нижнего плеча будут закрыты, поэтому в статическом

состоянии ток КМОП-микросхемой от источника питания потребляться не будет.

Условно-графическое изображение КМОП логического элемента «2И-НЕ» показано на рисунке 4, а таблица истинности

приведена в таблице 1. В таблице 1 входы обозначены как x 1 и x 2, а выход — F .

Рисунок 4. Условно-графическое изображение логического элемента «2И-НЕ»

Таблица 1. Таблица истинности КМОП-микросхемы, выполняющей

«2И-НЕ»

| x1 | x2 | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

«ИЛИ»

, выполненный

на КМОП транзисторах, представляет собой параллельное соединение ключей с электронным управлением. Отличие от упрощенной схемы

Отличие от упрощенной схемы

«2ИЛИ», рассмотренной ранее, заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику

питания. Вместо резистора в качестве нагрузки используются p-МОП транзисторы. Принципиальная схема

логического элемента «2ИЛИ-НЕ» , выполненного на комплементарных МОП-транзисторах приведена на рисунке 5.

Рисунок 5. Принципиальная схема логического элемента «ИЛИ-НЕ», выполненного на комплементарных МОП транзисторах

В схеме КМОП логического элемента «2ИЛИ-НЕ» в

качестве нагрузки используются последовательно включенные p-МОП транзисторы. В ней ток от источника питания на выход КМОП микросхемы будет

поступать только если все транзисторы в верхнем плече будут открыты, т.е. если сразу на всех входах будет присутствовать низкий потенциал

(). Если же хотя бы на одном из входов

будет присутствовать уровень логической единицы, то верхнее плечо двухтактного каскада, собранного на КМОП транзисторах, будет закрыто и ток

от источника питания поступать на выход КМОП-микросхемы не будет.

Таблица истинности логического элемента «2ИЛИ-НЕ» , реализуемая КМОП микросхемой, приведена в таблице 2, а

условно-графическое обозначение этих элементов приведено на рисунке 6.

Рисунок 6. элемента «2ИЛИ-НЕ»

Таблица 2. Таблица истинности МОП микросхемы, выполняющей логическую функцию «2ИЛИ-НЕ»

| x1 | x2 | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

В настоящее время именно КМОП-микросхемы получили наибольшее развитие. Причём наблюдается постоянная

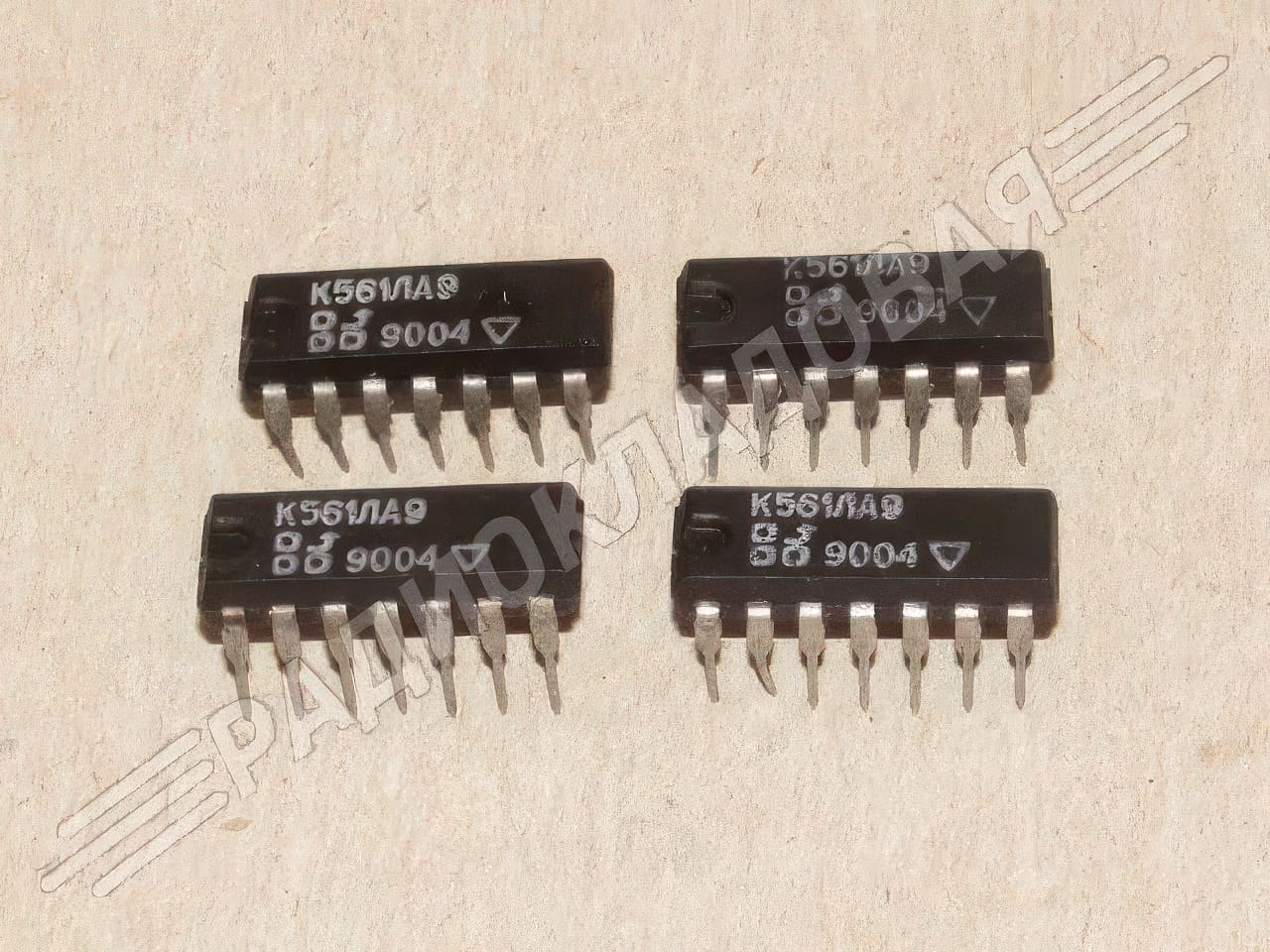

тенденция к снижению напряжения питания данных микросхем. Первые серии КМОП-микросхем, такие как К1561

(иностранный аналог C4000В) обладали достаточно широким диапазоном изменения напряжения питания (3..18В).

При этом при понижении напряжения питания у конкретной микросхемы понижается её предельная частота работы.

В дальнейшем, по мере совершенствования технологии производства, появились улучшенные КМОП-микросхемы с

лучшими частотными свойствами и меньшим напряжением питания, например, SN74HC.

Особенности применения КМОП-микросхем

Первой и основной особенностью КМОП-микросхем является большое входное сопротивление этих микросхем. В

результате на ее вход может наводиться любое напряжение, в том числе и равное половине напряжения питания,

и храниться на нём достаточно долго. При подаче на вход КМОП-элемента половины питания открываются транзисторы

как в верхнем, так и в нижнем плече выходного каскада, в результате микросхема начинает потреблять недопустимо

большой ток и может выйти из строя . Вывод: входы цифровых КМОП-микросхем ни в коем

случае нельзя оставлять неподключенными!

Второй особенностью КМОП-микросхем является то, что они могут работать при отключенном питании. Однако

работают они чаще всего неправильно. Эта особенность связана с конструкцией входного каскада. Полная

Полная

принципиальная схема КМОП-инвертора приведена на рисунке 7.

Рисунок 7. Полная принципиальная схема КМОП-инвертора

Диоды VD1 и VD2 были введены для защиты входного каскада от пробоя статическим электричеством. В то же самое время при

подаче на вход КМОП-микросхемы высокого потенциала он через диод VD1 попадёт на шину питания микросхемы, и так как она

потребляет достаточно малый ток, то КМОП микросхема начнёт работать. Однако в ряде случаев этого тока может не хватить для

питания микросхем. В результате КМОП микросхема может работать неправильно. Вывод: при неправильной работе КМОП микросхемы

тщательно проверьте питание микросхемы

, особенно выводы корпуса. При плохо пропаянном выводе отрицательного питания его

потенциал будет отличаться от потенциала общего провода схемы.

Четвёртая особенность КМОП-микросхем &mdash это протекание импульсного тока по цепи питания при ее переключении из

нулевого состояния в единичное и наоборот. В результате при переходе с

ТТЛ микросхем на КМОП микрохемы-аналоги резко увеличивается уровень помех. В ряде случаев это важно, и приходится отказываться

В ряде случаев это важно, и приходится отказываться

от применения КМОП микросхем в пользу или BICMOS микросхем.

Логические уровни КМОП-микросхем

Логические уровни КМОП-микросхем существенно отличаются от . При отсутствии тока нагрузки напряжение на выходе КМОП-микросхемы совпадает с напряжением

питания (логический уровень единицы) или с потенциалом общего провода (логический уровень нуля). При увеличении тока нагрузки

напряжение логической единицы может уменьшается до 2,8В (U п =15В) от напряжения питания. Допустимый уровень напряжения

на выходе цифровой КМОП микросхемы (серия микросхем К561) при пятивольтовом питании показан на рисунке 8.

Рисунок 8. Уровни логических сигналов на выходе цифровых КМОП-микросхем

Как уже говорилось ранее, напряжение на входе цифровой микросхемы по сравнению с выходом обычно допускается в больших

пределах. Для КМОП-микросхем договорились о 30% запасе. Границы уровней логического нуля и единицы для КМОП-микросхем

при пятивольтовом питании приведены на рисунке 9.

Рисунок 9. Уровни логических сигналов на входе цифровых КМОП-микросхем

При уменьшении напряжения питания границы логического нуля и логической единицы можно определить точно так же (разделить

напряжение питания на 3).

Семейства КМОП-микросхем

Первые КМОП-микросхемы не имели защитных диодов на входе, поэтому их монтаж представлял значительные трудности. Это семейство

микросхем серии К172. Следующее улучшенное семейство КМОП микросхем серии К176 получило эти защитные диоды. Оно достаточно распространено

и в настоящее время. Серия К1561 завершает развитие первого поколения КМОП микросхем. В этом семействе было достигнуто быстродействие

на уровне 90 нс и диапазон изменения напряжения питания 3 … 15В. Так как в настоящее время распространена

иностранная аппаратура, то приведу иностранный аналог этих КМОП микросхем — C4000В.

Дальнейшим развитием КМОП-микросхем стала серия SN74HC. Эти микросхемы отечественного аналога не имеют. Они

обладают быстродействием 27 нс и могут работать в диапазоне напряжений 2 . .. 6 В. Они

.. 6 В. Они

совпадают по цоколёвке и функциональному ряду с ,

но не совместимы с ними по логическим уровням, поэтому одновременно были разработаны КМОП микросхемы серии SN74HCT (отечественный

аналог — К1564), совместимые с ТТЛ микросхемами и по логическим уровням.

В это время наметился переход на трёхвольтовое питание. Для него были разработаны КМОП-микросхемы SN74ALVC с временем

задержки сигнала 5,5 нс и диапазоном питания 1,65 … 3,6 В. Эти же микросхемы способны работать

и при 2,5 вольтовом питании. Время задержки сигнала при этом увеличивается до 9 нс.

Наиболее перспективным семейством КМОП-микросхем в настоящее время считается семейство SN74AUC с временем задержки сигнала

1,9 нс и диапазоном питания 0,8 … 2,7 В.

Сокращение КМОП означает «комплементарный

МОП-транзистор». Также иногда используется сокращение COSMOS,

которое обозначает «комплементарная симметричная

МОП-структура». Логические элементы этого подсемейства строятся

как на «-канальных МОП-полевых транзисторах, так и на

/^-канальных МОП-полевых транзисторах. Схемы этого подсемейства

Схемы этого подсемейства

характеризуются ярко выраженной симметрией. При разработке схем

применяют только самозапирающиеся МОП-транзисторы (см. Бойт,

Электроника, ч. 2, разд. 8.2, МОП-полевые транзисторы).

Симметричность схем видна особенно хорошо в схеме элемента НЕ (рис.

6.91). Если на входе А действует Я-уровень, например +5 В, то

транзистор Т2 отпирается. На его истоке и подложке 0 В. Напряжение

затвор-исток UGS составляет +5 В. К истоку и подложке транзистора Тх

приложены +5 В.

Если к управляющему электроду также прикладываются +5 В, то

напряжение затвор-исток UGS = О В. Транзистор Тх заперт. Если Тх

заперт, а Т2 открыт, то выход элемента Z имеет уровень L (рис. 6.92).

Если на входе А действует i-уровень О В, то транзистор Т2 запирается и

напряжение затвор-исток UGS составляет О В. Напряжение затвор-исток

транзистора Ту UGS = —5 В, так как напряжение истока +5 В, а

затвора О В. Транзистор отпирается. Если Тх открыт, а Т2 заперт, выход

элемента Z имеет уровень Н.

В КМОП-НЕ-элементе всегда один транзистор открыт, а другой заперт.

Если на выходе элемента НЕ действует уровень 0, то элемент практически

не потребляет ток, так как Тх заперт. Если на выходе элемента НЕ

действует уровень Н, то элемент также практически не потребляет ток,

так как теперь Т2 заперт. Для управления последовательно включенными

элементами также не требуется ток, так как полевые транзисторы

практически не потребляют мощность. Только во время переключения от

источника питания потребляется небольшой ток, так как оба транзистора

одновременно, но недолго открыты. Один из транзисторов переходит из

открытого состояния в запертое и еще не полностью заперт, а другой

— из запертого в открытое и еще не полностью открыт. Также должны

перезарядиться транзисторные емкости.

Все КМОП-элементы устроены так, что в токовой ветви один транзистор

закрыт, а другой открыт. Энергопотребление КМОП-элементов крайне низко.

Оно зависит в основном от количества переключений в секунду или частоты

переключения.

КМОП-элементы отличаются малым энергопотреблением.

На рис. 6.93 изображена следующая типичная КМОП-схема. Если на обоих

входах действует уровень L, то транзисторы 7’ и Т2 будут открыты,

транзисторы Тг и Т4 заперты. Ту и Т2 при О В на А и В имеют UGS =

— 5 В, а Т3 и Т4 имеют UGS = О В. На выходе Z действует уровень Н.

Если на входе А действует уровень Н(+5 В), а на входе 5-уровень L (О

В), то Ту закрывается, а Т2 открывается. Путь от источника питания к

выходу Z блокирован запертым транзистором.

Одновременно отпирается транзистор Т3 и на выходе Z действует

примерно О В, то есть уровень L. Г4 заперт. Z всегда имеет уровень Z,

если по крайней мере на одном входе действует уровень Н.

Соответствующая схеме (рис. 6.93) рабочая таблица представлена на рис.

6.94. Схема производит при положительной логике операцию ИЛИ-НЕ.

Какую логическую операцию производит схема на рис. 6.95? Прежде всего

для схемы должна быть составлена рабочая таблица. Если на обоих входах

действуют Z-уровни (О В), то транзисторы Т{ и Т2 открываются (UGS =

— 5 В). -канального МОП-транзистора (рис. 6.97).

-канального МОП-транзистора (рис. 6.97).

Передаточный элемент работает как переключатель.

Если к Gx будет приложен уровень Н (например +5 В) и к G2 —

уровень L (О В), то оба транзистора запираются. В /ьканальном

МОП-транзисторе между управляющим электродом и подложкой приложено

напряжение О В. Образование проводящего канала между истоком и стоком

становится невозможным. Также и в я-канальном МОП-транзисторе между

управляющим электродом и подложкой приложено напряжение О В. Здесь

также не может возникнуть проводящий канал. Сопротивление между точками

А и Zдостигает нескольких сотен МОм.

Если на

Уровни на входах Gl и G2 всегда прикладываются в противофазе.

Управление может происходить с помощью элемента НЕ (рис. 6.99).

Получается двунаправленный ключ. У полевых транзисторов передаточного

элемента исток и сток могут взаимно менять свои функции. Поэтому вывод

затвора обозначается в середине его условной линии (рис. 6.99).

Интегрированные КМОП-микросхемы всегда содержат множество логических

элементов, которые могут быть использованы по отдельности или как

единая сложная логическая функция. На рис. 6.100 показана структура

На рис. 6.100 показана структура

схемы CD 4000 А. Эта схема содержит два элемента ИЛИ-HE с тремя входами

каждый и элемент НЕ. Схема CD 4012 А (рис. 6.101) содержит два элемента

И-НЕ с четырьмя входами каждый.

Интегральные схемы арифметических логических устройств содержат очень

много КМОП-элементов. На рис. 6.102 приведена схема 4-битного

сдвигающего регистра. Эта схема рассмотрена подробно в гл. 8.

Рис. 6.102. Схема КМОП-4-битного сдвигового регистра CD 4015 A (RCA)

Микросхема CD 4008 А является 4-битным полным сумматором. Полные

сумматоры рассматриваются подробно в гл. 10. Схема приведена здесь как

пример КМОП-схемотехники (рис. 6.103).

Интегральные микросхемы в КМОП-исполнении могут производиться с очень большой плотностью элементов,

Можно схему целого калькулятора уместить в одной микросхеме. Дальнейшее

совершенствование технологий ведет к повышению возможной плотности

компоновки.

Напряжение питания КМОП-элементов может колебаться в широком диапазоне.

Для серии CD-4000-A (рис. 6.100—6.103) фирма-производитель RCA

указывает диапазон напряжений питания от 3 В до 15 В. Типичные

передаточные характеристики при ряде напряжений питания показаны на

рис. 6.104.

Часто используются напряжения питания +5 В и +10 В. Для этих напряжений

питания на рис. 6.105 и 6.106 показаны диаграммы уровней. Для больших

напряжений питания характерна лучшая помехоустойчивость.

Разность между уровнями L и Н, отвечающая за помехоустойчивость, для

КМОП-схем составляет примерно от 30% до 40% напряжения питания.

В следующей таблице приведены важнейшие параметры КМОП-эле-ментов:

Рис. 6.103. Схема КМОП-4-битного полного сумматора CD 4008 A (RCA)

Наглядный пример тому, как всё сложно запутанно в определении приоритетов научно-исследовательских работ, это микросхемы КМОП и их появление на рынке.

Дело в том, что полевой эффект, который лежит в основе МОП-структуры был открыт ещё в конце 20-х годов прошлого века, но радиотехника тогда переживала бум вакуумных приборов (радиоламп) и эффекты, обнаруженные в кристаллических структурах, были признаны бесперспективными.

Затем в 40-е годы практически заново был открыт биполярный транзистор, а уже потом, когда дальнейшие исследования и усовершенствования биполярных транзисторов показали, что это направление ведёт в тупик, учёные вспомнили про полевой эффект.

Так появился МОП-транзистор , а позднее КМОП-микросхемы. Буква К

в начале аббревиатуры означает комплементарный, то есть дополняющий. На практике это означает, что в микросхемах применяются пары транзисторов с абсолютно одинаковыми параметрами, но один транзистор имеет затвор n-типа, а другой транзистор имеет затвор p-типа. На зарубежный манер микросхемы КМОП называют CMOS

(Complementary Metal-Oxide Semiconductor). Также применяются сокращения КМДП, К-МОП.

Среди обычных транзисторов примером комплементарной пары являются транзисторы КТ315 и КТ361.

Сначала на рынке радиоэлектронных компонентов появилась серия К176 основанная на полевых транзисторах, и, как дальнейшее развитие этой серии, была разработана ставшая очень популярной серия К561. Эта серия включает в себя большое количество логических микросхем.

Эта серия включает в себя большое количество логических микросхем.

Поскольку полевые транзисторы не так критичны к напряжению питания, как биполярные, эта серия питается напряжением от +3 до +15V. Это позволяет широко использовать эту серию в различных устройствах, в том числе и с батарейным питанием. Кроме того, устройства собранные на микросхемах серии К561, потребляют очень маленький ток. Да и не мудрено, ведь основу КМОП-микросхем составляет полевой МДП-транзистор.

Например, микросхема К561ТР2 содержит четыре RS-триггера и потребляет ток 0,14 mA, а аналогичная микросхема серии К155 потребляла минимум 10 — 12 mA. Микросхемы на КМОП структурах обладают очень большим входным сопротивлением, которое может достигать 100 МОм и более, поэтому их нагрузочная способность достаточно велика. К выходу одной микросхемы можно подключить входы 10 — 30 микросхем. У микросхем ТТЛ такая нагрузка вызвала бы перегрев и выход из строя.

Поэтому конструирование узлов на микросхемах с применением КМОП транзисторов позволяет применять более простые схемные решения, чем при использовании микросхем ТТЛ.

За рубежом наиболее распространённый аналог серии К561 маркируется как CD4000. Например, микросхеме К561ЛА7 соответствует зарубежная CD4011.

Используя микросхемы серии К561, не следует забывать о некоторых нюансах их эксплуатации. Следует помнить, что хотя микросхемы работоспособны в большом диапазоне напряжений, при снижении напряжения питания падает помехоустойчивость, а импульс слегка «расползается». То есть чем напряжение питания ближе к максимуму, тем круче фронты импульсов.

На рисунке показан классический базовый элемент (вентиль), который осуществляет инверсию входного сигнала (элемент НЕ). То есть если на вход приходит логическая единица, то с выхода снимается логический ноль и наоборот. Здесь наглядно показана комплементарная пара транзисторов с затворами «n» и «p» типов.

На следующем рисунке показан базовый элемент 2И — НЕ. Хорошо видно, что резисторы, которые присутствуют в аналогичном элементе ТТЛ микросхемы, здесь отсутствуют. Из двух таких элементов легко получить триггер, а из последовательного ряда триггеров прямая дорога к счётчикам, регистрам и запоминающим устройствам.

При всех положительных качествах интегральных микросхем серии К561 у них, конечно, есть и недостатки. Во-первых, по максимальной рабочей частоте КМОП микросхемы заметно уступают микросхемам с другой логикой и работающей на биполярных транзисторах.

Частота, на которой уверенно работает серия К561, не превышает 1 МГц. Для согласования микросхем основанных на МОП структурах с другими сериями, например, ТТЛ, применяются преобразователи уровня К561ПУ4, К561ЛН2 и другие. Эти микросхемы также синхронизируют быстродействие, которое у разных серий может отличаться.

Но самый большой недостаток микросхем на комплементарных МОП структурах, это сильнейшая чувствительность микросхемы к статическому электричеству. Поэтому на заводах и лабораториях оборудуются специальные рабочие места. На столе все работы производятся на металлическом листе, который подключён к общей шине заземления. К этой шине подключается и корпус паяльника, и металлический браслет, одеваемый на руку работнику.

Некоторые микросхемы поступают в продажу упакованные в фольгу, которая закорачивает все выводы между собой. При работе в домашних условиях также необходимо найти возможность для стекания статического заряда хотя бы на трубу отопления. При монтаже первыми распаиваются выводы питания, а уже затем все остальные.

Рис.

16.10.

Принципиальное отличие КМОП-схем от nМОП-технологии заключается в отсутствии в схеме активных сопротивлений. К каждому входу схемы подключена пара транзисторов с различным типом канала. Транзисторы с каналом p-типа подключены подложкой к источнику питания, поэтому образование канала в них будет происходить при достаточной большой разности потенциалов между подложкой и затвором, причем потенциал

на затворе должен быть отрицательным относительно подложки. Такое состояние обеспечивается подачей на затвор потенциала земли (т.е. логического 0

). Транзисторы с каналом n-типа подключены подложкой к земле, поэтому образование канала в них будет происходить при подаче на затвор потенциала источника питания (т. е. логической 1

е. логической 1

). Одновременная подача на такие пары транзисторов с разным типом каналов логического нуля или логической единицы приводит к тому, что один транзистор

пары обязательно будет открыт, а другой закрыт. Таким образом, создаются условия к подключению выхода либо к источнику п

итания, либо к земле.

Так, в простейшем случае, для схемы инвертора (рис. 16.10) при А=0

транзистора VT1 будет открыт, а VT2 закрыт. Следовательно, выход

схемы F

будет подключен через канал VT1 к источнику питания, что соответствует состоянию логической единицы: F=1

. При А=1

транзистор

VT1 будет закрыт (на затворе и подложке одинаковые потенциалы), а VT2 открыт. Следовательно, выход

схемы F

будет подключен через канал транзистора VT2 к земле. Это соответствует состоянию логического нуля: F=0

.

Логическое сложение

(рис. 16.11) осуществляется за счет последовательного соединения p-каналов транзисторов VT1 и VT2. При подаче хотя бы одной единицы единого канала у данных транзисторов не образуется. В то же время благодаря параллельному соединению VT3 и VT4 осуществляется открытие соответствующего транзистора в нижней части схемы, обеспечивающее подключение выхода F к земле. Получается F=0 при подаче хотя бы одной логической 1 – это правило ИЛИ-НЕ.

В то же время благодаря параллельному соединению VT3 и VT4 осуществляется открытие соответствующего транзистора в нижней части схемы, обеспечивающее подключение выхода F к земле. Получается F=0 при подаче хотя бы одной логической 1 – это правило ИЛИ-НЕ.

Рис.

16.11.

Функция

И-НЕ осуществляется за счет параллельного соединения VT1 и VT2 в верхней части схемы и последовательного соединения VT3 и VT4 в нижней части (рис. 16.12). При подаче хотя бы на один вход нуля единый канал на VT3 и VT4 не образуется, выход

будет отключен от земли. В то же время хотя бы один транзистор

в верхней части схемы (на затвор которого подан логический

ноль) будет обеспечивать подключение выхода F

к источнику питания: F=1

при подаче хотя одного нуля – правило И-НЕ.

Рис.

16.12.

Краткие итоги

В зависимости от элементной базы, различают различные технологии производства ИМС. Основными являются ТТЛ на биполярных транзисторах и nМОП и КМОП на полевых транзисторах

.

Ключевые термины

nМОП-технология

полевых транзисторов

с индуцированным каналом n-типа.

Буфер на 3 состояния

– выходная часть схемы ТТЛ, обеспечивающая возможность перехода в третье, высокоимпедансное состояние.

КМОП-технология

— технология производства ИМС на базе полевых транзисторов

с каналами обоих типов электропроводности.

Открытый коллектор

– вариант реализации буферной части элементов ТТЛ без резистора в цепи нагрузки, который выносится за пределы схемы.

Схемы с активной нагрузкой

– схемы ТТЛ, в которых состояние буферной цепи определяется состоянием не одного, а двух транзисторов.

Транзисторно-транзисторная логика

– технология производства ИМС на базе биполярных транзисторов.

Принятые сокращения

КМОП –

комплементарный, металл, оксид, полупроводник

Набор для практики

Упражнения к лекции 16

Упражнение 1

Вариант 1 к упражнению 1

. Нарисовать схему 3-входового элемента ИЛИ-НЕ по nМОП-технологии.

Нарисовать схему 3-входового элемента ИЛИ-НЕ по nМОП-технологии.

Вариант 2 к упражнению 1

.Нарисовать схему 3-входового элемента И-НЕ по nМОП-технологии.

Вариант 3 к упражнению 1

.Нарисовать схему 4-входового элемента ИЛИ-НЕ по nМОП-технологии.

Упражнение 2

Вариант 1 к упражнению 2

.Нарисовать схему 3-входового элемента ИЛИ-НЕ по КМОП-технологии.

Вариант 2 к упражнению 2

.Нарисовать схему 3-входового элемента И-НЕ по КМОП-технологии.

Вариант 3 к упражнению 2

.Нарисовать схему 4-входового элемента ИЛИ-НЕ по КМОП-технологии.

Упражнение 3

Вариант 1 к упражнению 3

.Нарисовать схему 3-входового элемента ИЛИ-НЕ по ТТЛ-технологии.

Вариант 2 к упражнению 3

.Нарисовать схему 3-входового элемента И-НЕ по ТТЛ-технологии.

Вариант 3 к упражнению 3

.Нарисовать схему 4-входового элемента ИЛИ-НЕ по ТТЛ-технологии.

Упражнение 4

Вариант 1 к упражнению 4

. Нарисовать схему 3-входового элемента ИЛИ по nМОП-технологии.

Нарисовать схему 3-входового элемента ИЛИ по nМОП-технологии.

Вариант 2 к упражнению 4

.Нарисовать схему 3-входового элемента И по nМОП-технологии.

Вариант 3 к упражнению 4

.Нарисовать схему 4-входового элемента ИЛИ по nМОП-технологии.

Упражнение 5

Вариант 1 к упражнению 5

.Нарисовать схему 3-входового элемента ИЛИ по КМОП-технологии.

Вариант 2 к упражнению 5

.Нарисовать схему 3-входового элемента И по КМОП-технологии.

Вариант 3 к упражнению 5

.Нарисовать схему 4-входового элемента ИЛИ по КМОП-технологии.

Упражнение 6

Вариант 1 к упражнению 6

.Нарисовать схему 3-входового элемента ИЛИ по ТТЛ-технологии.

Вариант 2 к упражнению 6

.Нарисовать схему 3-входового элемента И по ТТЛ-технологии.

Вариант 3 к упражнению 6

.Нарисовать схему 4-входового элемента ИЛИ по ТТЛ-технологии.

Упражнение 7

Вариант 1 к упражнению 7

.Нарисовать схему элемента 2И-ИЛИ-НЕ по ТТЛ-технологии.

Вариант 2 к упражнению 7

.Нарисовать схему элемента 2И-ИЛИ-НЕ по КМОП-технологии.

Вариант 3 к упражнению 7

.Нарисовать схему элемента 2И-ИЛИ-НЕ по nМОП-технологии.

Упражнение 8

Вариант 1 к упражнению 8

.Нарисовать схему 3-входового элемента ИЛИ-НЕ с буфером на 3 состояния.

Вариант 2 к упражнению 8

.Нарисовать схему 3-входового элемента И-НЕ с открытым коллектором.

Вариант 3 к упражнению 8

.Нарисовать схему 3-входового элемента ИЛИ с буфером на 3 состояния.

Комплементарная МОП логика (КМОП — КМДП -CMOS — Complementary Metal-Oxide-Semiconductor) сегодня является основной в производстве больших интегральных схем микропроцессорных комплектов, микроконтроллеров, СБИС персональных компьютеров, ИС памяти. Кроме ИС высокой интеграции для создания электронного обрамления БИС и несложных электронных схем выпущено несколько поколений КМОП серий малой и средней интеграции. В основе лежит рассмотренный ранее инвертор (рис 2. 9) на комплементарных (взаимодополняющих) МОП транзисторах с индуцированным каналом разной проводимости p и n типа, выполненных на общей подложке (входные охранные цепочки не показаны).

9) на комплементарных (взаимодополняющих) МОП транзисторах с индуцированным каналом разной проводимости p и n типа, выполненных на общей подложке (входные охранные цепочки не показаны).

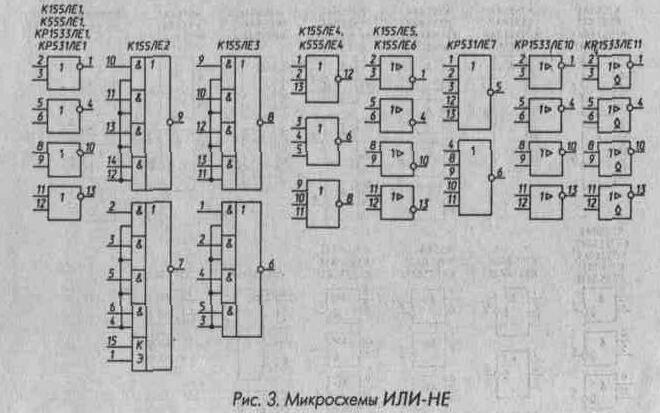

Рис 3.8. Двухвходовые КМОП логические элементы а) И-НЕ, б) ИЛИ-НЕ

Как и в случае простого инвертора, особенностью ЛЭ является наличие двух ярусов транзисторов относительно выходного вывода. Логическая функция, выполняемая всей схемой, определяется транзисторами нижнего яруса. Для реализации И-НЕ в положительной логике транзисторы с n-каналом включаются последовательно друг с другом, с p-каналом – параллельно, а для реализации ИЛИ-НЕ – наоборот (Рис 3.8).

Микросхемы КМОП-структуры близки к идеальным ключам: в статическом режиме они практически не потребляют мощности, имеют большое входное и малое входное сопротивления, высокую помехозащищенность, большую нагрузочную способность, хорошую температурную стабильность, устойчиво работают в широком диапазоне питающих напряжений (от +3 до +15 В). Выходной сигнал практически равен напряжению источника питания. При Еп=+5В обеспечивается совместимость логических уровней со стандартной ТТЛ/ТТЛШ-логикой. Пороговое напряжение при любом напряжении питания равно половине напряжения питания U пор = 0,5 Еп, что обеспечивает высокую помехоустойчивость.

Выходной сигнал практически равен напряжению источника питания. При Еп=+5В обеспечивается совместимость логических уровней со стандартной ТТЛ/ТТЛШ-логикой. Пороговое напряжение при любом напряжении питания равно половине напряжения питания U пор = 0,5 Еп, что обеспечивает высокую помехоустойчивость.

Логические элементы с большим числом входов организованы подобным же образом. В номенклатуре микросхем КМОП есть ЛЭ И, ИЛИ, И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ, с количеством входов до 8. Увеличить число входных переменных можно с помощью дополнительных логических элементов, принадлежащих к той же серии ИС.

Отечественная промышленность выпускает несколько универсальных КМОП серий: К164, К176, К561, К564, К1561, К1564.

К176 – стандартная КМОП t з =200 нс, I пот £100 мкА

К564, К561, К1561 – усовершенствованная КМОП t з =15 нс (15 В), I пот =1-100 мкА

К1564 – высокоскоростная КМОП (функциональный аналог серии 54HC) t з =9-15 нс, Uпит=2-6 В, I пот £10 мкА

Основные технические характеристики ИС серии К564 (К561) приведены ниже:

Напряжение питания U п, В …………………………. .3-15

.3-15

Мощность потребления

В статическом режиме, мкВт/корпус …………0,1

При f=1 МГц, U п =10 В, С н =50 пф, мвт ……….20

Допустимая мощность рассеивания. Мвт/корпус …..500

Входное напряжение, В ……………….от -0,5В до U п + 0,5В

Выходное напряжение, В

Низкого уровня ………………………… не более 0,05В,

Высокого уровня …………………не менее U п + 0,5В

Средняя задержка распространения сигнала при С н =15 нф

Для U п =+5 В, нс ………………………………50

Для U п =+10 В, нс ……………………………..20,

Рабочая температура, 0 С

Серия 564 ………………………..от -60 до +125

Серия К561 ……………………….от -40 до +85

Если развитие ТТЛ-серий, главным образом, шло в сторону уменьшения энергопотребления, то КМОП-серии развивались в направлении повышения быстродействия. В конце концов, победила КМОП-технология. Последующие поколения стандартной логики выпускаются уже только по ней. Таким образом, второе поколение микросхем стандартной логики выпускается по КМОП-технологии, но сохраняет полное функциональное соответствие с ТТЛ-сериями.

Мой компьютер на логических микросхемах / Хабр

Привет, Хабр. Два года назад, как раз перед началом пандемии, я затеял большой проект: построить компьютер, используя только простые логические микросхемы 74 серии и микросхемы памяти. В этой статье я бы хотел кратко рассказать о том, что получилось, и более подробно об основной части – процессоре.

На сегодняшний день можно сказать, что у меня получился полноценный компьютер: на нем можно играть, можно читать и редактировать текстовые файлы на SD-карте, можно считать и даже строить графики. Нельзя только выходить в интернет.

Технические характеристики компьютера получились следующие:

Процессор: 8 бит, 4 регистра, очень урезанный набор инструкций, тактовая частота 1.5 МГц;

Память: 32 кБ ПЗУ и 52 кБ ОЗУ;

Видеокарта: текстовый режим 80×30, 16 цветов (как в CGA), подключение к VGA-монитору;

Внешний накопитель — SD-карта с файловой системой FAT16;

Разъем PS/2 для подключения клавиатуры.

Процессор

Процессор состоит из трех плат

В этом разделе я попытаюсь показать ход моих мыслей при проектировании процессора и покажу, что из этого вышло.

Мне хотелось, чтобы получился более-менее полноценный процессор, программировать который было бы не слишком большой болью. То есть, должны быть полновесные 8 бит и небольшой, но не слишком урезанный набор арифметики: обязательно должны быть простые действия вроде сложения-вычитания с переносом и без и все логические операции, но умножение – это уже слишком. Стеком и прерываниями тоже можно смело пожертвовать.

С такими требованиями к арифметике АЛУ легко сделать асинхронным: при подаче значений на входы на выходе сразу появится результат. Чтобы не было слишком много проводов, один вход АЛУ можно привязать к одному конкретному регистру, который обычно называют аккумулятором.

Следующий вопрос – как сделать переходы. Чтобы процессор выполнил инструкцию jmp label (переход на заданный в инструкции адрес), нужно сначала загрузить адрес в какой-то регистр, а потом уже оттуда передать его в IP. Загружать напрямую в IP нельзя: адрес состоит из двух байт, и когда будет загружен первый байт, мы не сможем загрузить второй, потому что в IP будет уже наполовину новый адрес.

Загружать напрямую в IP нельзя: адрес состоит из двух байт, и когда будет загружен первый байт, мы не сможем загрузить второй, потому что в IP будет уже наполовину новый адрес.

С доступом к памяти та же история: в x86, например, можно сделать так: mov ax, [label]. Здесь, чтобы загрузить из памяти значение по закодированному в инструкции адресу, этот адрес тоже нужно сначала поместить в невидимый регистр.

Раз для адресации нужен отдельный регистр, почему бы не сделать его доступным программисту? Тогда можно будет явно загружать туда значения и выполнять с ними арифметику, а потом использовать их в качестве адреса перехода и операций с памятью. Назовем этот регистр P. Так как адрес 16-битный, а данные 8-битные, разделим P на две части: PL и PH.

Итак, минимум нужно три регистра, доступных программисту: аккумулятор A для фиксированного подключения к одному из входов АЛУ и пара PL/PH для адресации. Кодировать три регистра в инструкции неудобно: нужно два бита, остается одна неиспользуемая комбинация, поэтому добавим еще один регистр B.

Из-за того, что адрес нужно загружать в P явно, для операций с памятью и перехода потребуется больше одной инструкции. Например, переход:

ldi pl, lo(label) ; загрузка младшего байта адреса в PL

ldi ph, hi(label) ; загрузка старшего байта в PH

jmp ; собственно переход - инструкция без аргументов!Заметим, что у нас появилось два 16-битных регистра: указатель инструкции IP и указатель адреса P, причем из P нужно уметь передавать значение в IP. Для передачи значения не обязательно копировать его: можно добавить флаг, определяющий, какой из физических регистров будет действовать как IP, а какой как P. При исполнении инструкции перехода этот флаг будет переключаться, и с точки зрения программиста окажется так, что после перехода в P будет адрес возврата! Таким образом получится сделать вызовы функций без использования стека: достаточно будет в начале функции сохранить значение из P, а при возврате считать его и выполнить переход.

Как выглядят пролог и эпилог функции

function:

mov a, ph ; арифметика (включая mov) возможна только между A и другим регистром

mov b, a

mov a, pl

ldi ph, hi(ret_addr)

ldi pl, lo(ret_addr)

st a ; сначала сохраняем младший байт

inc pl ; ret_addr выровнен, поэтому переполнения через 256 не случится

st b

; . .. тут сам код функции

ldi ph, hi(ret_addr)

ldi pl, lo(ret_addr)

ld a

inc pl

ld ph ; старший байт можно загрузить сразу в PH

mov pl, a

jmp ; возврат из функции

; в секции данных:

.align 2

ret_addr: res 2 ; резервируем два байта для адреса возврата

.. тут сам код функции

ldi ph, hi(ret_addr)

ldi pl, lo(ret_addr)

ld a

inc pl

ld ph ; старший байт можно загрузить сразу в PH

mov pl, a

jmp ; возврат из функции

; в секции данных:

.align 2

ret_addr: res 2 ; резервируем два байта для адреса возвратаТеперь, когда регистры определены, можно нарисовать общую схему процессора.

Основные блоки процессора

Здесь мы видим регистры A и B, блок регистров P, содержащий в себе две пары регистров: PL/PH и IP, регистр текущей инструкции IR, регистр флагов и АЛУ (блок в форме надкушенной трапеции).

Для мультиплексирования сигналов на шинах я использую логические сигналы с тремя состояниями. В каждый момент времени на конкретной шине активно только одно устройство, определяющее уровни сигналов, остальные же находятся в состоянии высокого сопротивления.

Красная шина на схеме – это внешняя шина данных, ведущая к памяти и перефирийным устройствам. Данные с нее могут быть напрямую загружены в регистр инструкции IR или через буфер (треугольник под IR на схеме) переданы на внутреннюю шину процессора (зеленая), ведущую на входы всех регистов. АЛУ также выводит свой результат на зеленую шину.

Данные с нее могут быть напрямую загружены в регистр инструкции IR или через буфер (треугольник под IR на схеме) переданы на внутреннюю шину процессора (зеленая), ведущую на входы всех регистов. АЛУ также выводит свой результат на зеленую шину.

Розовая шина ведет на второй вход АЛУ. Если ни одно из устройств, подключенных к ней, не активно, на этой шине будет ноль благодаря подтягивающим резисторам. Это позволяет использовать ноль вместо регистра в качестве операнда арифметичских инструкций. Например, так: adc a, 0.

И, наконец, голубая шина, ведущая от блока P наружу – шина адреса. На ней процессор выставляет адрес памяти, чтобы записать или считать данные.

У регистров A и B по два выхода: на внешнюю шину данных и на АЛУ. Таким образом эти регистры могут участвовать в арифметике и быть загруженными в память. Регистры PL и PH не могут быть загружены в память напрямую: это не имеет смысла, ведь они хранят адрес операции с памятью.

Конечно, почти все блоки на этой схеме – это не отдельные микросхемы. Например, для регистра B нужно три микросхемы: собственно восьмибитный регистр 74HC273 и два выходных буфера 74HC244. Для каждой пары регистров из P нужно восемь микросхем: четыре четырехбитных счетчика 74HC161 и четыре буфера 74HC244.

Например, для регистра B нужно три микросхемы: собственно восьмибитный регистр 74HC273 и два выходных буфера 74HC244. Для каждой пары регистров из P нужно восемь микросхем: четыре четырехбитных счетчика 74HC161 и четыре буфера 74HC244.

Плата модуля регистров

Адресное пространство

Как вы могли заметить, процессор адресует максимум 216 Байт = 64 кБ, но памяти на самом деле больше: 32 кБ ПЗУ и 52 кБ ОЗУ. Такое возможно с помощью переключения банков: по умолчанию в нижние 32 кБ отображается ПЗУ, но если записать нужный бит в регистр конфигурации памяти, можно отобразить туда дополнительную оперативку. Это позволяет делать довольно сложные приложения: из-за крайне низкой плотности кода 32 кБ едва хватает на драйвер файловой системы, поэтому без переключения банков текстовый редактор, например, ну никак не получилось бы написать. А так можно загрузить приложение с SD-карты в нижнюю часть ОЗУ и использовать функции работы с файловой системой из ПЗУ как системные вызовы.

Плата модуля памяти

На старшие сегменты адресного пространства отображены видеопамять и регистры периферийных устройств (клавиатуры и SD-карты), а также регистр конфигурации памяти. Видеопамять организована в два отдельных сегмента для цвета и для текста, в отличие от CGA, где цвета перемежаются с символами. Такая организация проще: чтобы вывести строку, можно просто побайтово скопировать ее. Или, например, можно легко очистить часть экрана, оставив информацию о цвете.

Процесс разработки

Для разработки я использовал только свободное ПО (кроме текстового редактора). После определения общей структуры модуля я рисовал желаемые тайминги сигналов и по ним описывал модели и тесты на языке Verilog, которые запускал и проверял с помощью Icarus Verilog и GTKWave. Потом по списку микросхем 7400 серии я выбирал подходящие и смотрел, есть ли они в продаже. Когда микросхемы были выбраны, я переделывал код с использованием моделей конкретных микросхем. Одновременно я рисовал схему в KiCAD. Таким образом получалось полное соответствие между схемой и моделью и можно было быть уверенным (почти), что всё заработает в железе.

Таким образом получалось полное соответствие между схемой и моделью и можно было быть уверенным (почти), что всё заработает в железе.

Такой подход оправдал себя: в платах почти не было логических ошибок. Возникали другие непредвиденные проблемы: например, благодаря этому проекту я узнал про наводки между соседними дорожками и про отражение высокочастотных сигналов и про то, что будет, если этого не учитывать. Также я узнал, что более быстрая серия микросхем не значит лучшая.

Заключение

Этот пост получился уже довольно длинным, а я многого не рассказал: про видеокарту, про АЛУ, про кодирование инструкций и ассемблер, про общение с PS/2 и SD-картой, а также про программную часть этого карантинного проекта. Если будет интересно, напишу еще посты, а пока можете посмотреть репозиторий.

UPD следующий пост про кодирование и исполнение инструкций

UPD пост про видеокарту

UPD пост про АЛУ

Логический элемент — «И-НЕ» » Паятель.Ру

Если, для того чтобы на выходе логического элемента «ИЛИ-НЕ» была единица нужно чтобы нули были поданы на все его входы, а для получения на выходе нуля нужно чтобы единица была хотя бы на одном из входов, то для «И-НЕ» ситуация обратная: Логический ноль на выходе элемента «И-НЕ» будет только тогда, когда на все его входы будут поданы единицы. А для получения на выходе элемента «И-НЕ» единицы, нужно чтобы хотя бы на один из входов был подан уровень логического нуля.

А для получения на выходе элемента «И-НЕ» единицы, нужно чтобы хотя бы на один из входов был подан уровень логического нуля.

Рассмотрим в чем это выражается на практике. Для этого нужен модуль конструктора «Логика» с четырьмя элементами «2И-НЕ» (рис. 1). Соберем схему, показанную на рисунке 2. В схеме использован модуль с элементами «2И-НЕ».

S1 и S2 — кнопки, включая кнопку мы на вход элемента подаем логическую единицу. При этом зажигается соответствующий светодиод (HL1, HL2). Состояние выхода показывает светодиод HL3 — горит тогда когда на выходе единица.

Проверим логику «2И-НЕ» -пока кнопки S1 и S2 не нажаты (на входах нули), — на выходе единица (горит HL3). Если нажать любую из кнопок, -состояние не меняется. Чтобы оно изменилось нужно нажать обе кнопки сразу, и тогда на выходе будет ноль.

А теперь посмотрим, как будет работать мультивибратор, собранный на элементах «2И-НЕ» (рис. 3). И работает почти так же. Разница в том, что для того чтобы этот мультивибратор работал (чтобы мигал светодиод HL1) нужно чтобы тумблеры S1 и S2 были включены (а в схеме на «2ИЛИ-НЕ» они должны были быть выключенными).

Если один из этих тумблеров (или оба) выключить, мультивибратор перестанет генерировать. В схеме на «2ИЛИ-НЕ» для того чтобы мультивибратор перестал генерировать тумблеры нужно было включать.

В общем, понятно, — логика обратная. Если в схеме мультивибратора на «2ИЛИ-НЕ», чтобы прекратить генерацию нужно на вход элемента подать единицу, то в схеме на «2И-НЕ» для прекращения генерации на вход нужно подать нуль.

Рис.4

Соберем эту схему, на элементах «2И-НЕ» (рис. 4), и сигнализатор высыхания почвы превратится в сигнализатор затопления подвала, так как его логика действия будет противоположной.

Рассмотрим эту схему. Как и ранее, Это мультивибратор, вырабатывающий импульсы звуковой частоты, на выходе которого подключен пьезоэлектрический звукоизлучатель BF1. Схема управления, как и прежде, состоит из датчика — двух металлических гвоздей или винтов и переменного резистора R2, которым можно регулировать его чувствительность. Винты должны быть, скажем, воткнуты в землю или просто лежат на полу подвала, на некотором расстоянии друг от друга.

Когда в подвале сухо сопротивление среды между винтами значительно больше сопротивления R2. Напряжение на R2 держится на уровне логического нуля и, поэтому, мультивибратор не работает.

Если подвал будет затоплен водой, сопротивление между винтами будет значительно ниже сопротивления R2, и на резисторе R2 напряжение поднимется до уровня логической единицы. Это позволит мультивибратору работать, и из BF1 раздастся звук.

Рис.5

Как же сделать так, чтобы наш индикатор затопления подвала снова превратился в индикатор высыхания почвы? Просто! Нужно всего-то поменять местами датчик и R2, — сделать так, как показано на рис. 5.

Чтобы сигнализатор начал звучать нужно на второй вход верхнего по схеме элемента «2И-НЕ» подать единицу, а чтобы он замолчал, — нуль. Когда в цветочном горшке сухо, сопротивление между винтами (рис. 5) значительно больше сопротивления R2. Значит, на этом входе элемента будет единица, -сигнализатор звучит. Полили почву, — сопротивление между винтами датчика резко снизилось и стало значительно ниже сопротивления R2. Теперь на входе элемента будет ноль, — звучание прекратилось.

Теперь на входе элемента будет ноль, — звучание прекратилось.

Логика работы RS-триггера (рис. 6), сделанного на элементах «2И-НЕ» тоже претерпит значительные изменения. Теперь переключать триггер нужно не логическими единицами, а логическими нулями. Именно поэтому кнопки S1 и S2 подключены по-другому, так чтобы при нажатии кнопки на вход логического элемента поступал низкий уровень (логический 0).

Рис.6

определение микросхем по The Free Dictionary

Эти услуги и расходные материалы напрямую поддерживают инициативы DLA по предотвращению подделки, программы проверки и тестирования продукции, специфичные для микросхем FSC 5962, действующих в Агентстве. Вступает в силу с выпуском данных индекса цен производителей (PPI) за июль 2018 г. 9 августа 2018 г., Бюро Департамент статистики труда начал использовать гедонистическое моделирование для оценки скорректированных с учетом качества цен на микропроцессоры для ноутбуков в рамках индексов PPI для интегрированных микросхем: также известный как QML Class Y, сертификация признана высшей гарантией качества и надежности для керамических негерметично закрытых Микросхемы Flip-Chip для аэрокосмической и оборонной промышленности. От физических механизмов и воздействия космоса на микросхемы и стратегий проектирования для борьбы с космическим излучением до специального исследовательского оборудования и технологических особенностей диодов, схем и эффектов различного излучения на каждом из них — все это заполнено диаграммами, графиками, расчетами допусков и дискуссии, необходимые для любого проекта создания космической электроники. Помимо основного материала о современных подходах к разработке и применению элементной микроэлектронной базы бортового радиоэлектронного оборудования на космических аппаратах, систем двойного и специального назначения, Белоус, Саладуха, и Шведов предоставляют обширную справочную информацию и вспомогательные материалы, такие как конфигурация современных космических аппаратов, роль бортового электронного оборудования в достижении цели проекта, статистика аварий и отказов космических аппаратов, причины широкого использования поддельных микросхем в России и способы остановить это, а также воздействие ионизирующего космического излучения и потока высоких напряжений Скорость и высокоэнергетические микрочастицы (космическая пыль) на радиоэлектронном оборудовании в космических приложениях.

От физических механизмов и воздействия космоса на микросхемы и стратегий проектирования для борьбы с космическим излучением до специального исследовательского оборудования и технологических особенностей диодов, схем и эффектов различного излучения на каждом из них — все это заполнено диаграммами, графиками, расчетами допусков и дискуссии, необходимые для любого проекта создания космической электроники. Помимо основного материала о современных подходах к разработке и применению элементной микроэлектронной базы бортового радиоэлектронного оборудования на космических аппаратах, систем двойного и специального назначения, Белоус, Саладуха, и Шведов предоставляют обширную справочную информацию и вспомогательные материалы, такие как конфигурация современных космических аппаратов, роль бортового электронного оборудования в достижении цели проекта, статистика аварий и отказов космических аппаратов, причины широкого использования поддельных микросхем в России и способы остановить это, а также воздействие ионизирующего космического излучения и потока высоких напряжений Скорость и высокоэнергетические микрочастицы (космическая пыль) на радиоэлектронном оборудовании в космических приложениях. В году, закончившемся 31 декабря 2015 года, компания, которая занимается разработкой, производством и продажей пассивных электронных компонентов, известных как резисторы, и гибридных микросхем, продала 32,9 млн. Фунтов стерлингов по сравнению с 39,2 млн. Фунтов стерлингов годом ранее. Сертификация проводных соединений (25-27 августа, Вифлеем, Пенсильвания), Сертификация процессов и выявление дефектов: гибриды, микросхемы и модули RF / MMIC (15-18 сентября, Пасадена, Калифорния) и технология упаковки в микроволновой печи (7-9 декабря, Сан-Диего, Калифорния) .CML Microcircuits (Maldon, Essex) выпустила процессор общей платформы PMR для поддержки цифровых / аналоговых систем FDMA PMR / LMR и 2-слотовых цифровых систем TDMA.Компании, упомянутые в этом отчете: Америка, APAC, EMEAKey Vendors, Cirrus Logic, STMicroelectronics, Texas Instruments, Wolfson Micro, Analog Devices, AMS, Broadcom, CML Microcircuits, Conexant, Exstreamer, Integrated Device Technology, Maxim Integrated Исследователи показывают, что слабая связь обеспечивает каркас пресинаптической пластичности, отличительный признак синаптической передачи сигналов в микросхемах гиппокампа.

В году, закончившемся 31 декабря 2015 года, компания, которая занимается разработкой, производством и продажей пассивных электронных компонентов, известных как резисторы, и гибридных микросхем, продала 32,9 млн. Фунтов стерлингов по сравнению с 39,2 млн. Фунтов стерлингов годом ранее. Сертификация проводных соединений (25-27 августа, Вифлеем, Пенсильвания), Сертификация процессов и выявление дефектов: гибриды, микросхемы и модули RF / MMIC (15-18 сентября, Пасадена, Калифорния) и технология упаковки в микроволновой печи (7-9 декабря, Сан-Диего, Калифорния) .CML Microcircuits (Maldon, Essex) выпустила процессор общей платформы PMR для поддержки цифровых / аналоговых систем FDMA PMR / LMR и 2-слотовых цифровых систем TDMA.Компании, упомянутые в этом отчете: Америка, APAC, EMEAKey Vendors, Cirrus Logic, STMicroelectronics, Texas Instruments, Wolfson Micro, Analog Devices, AMS, Broadcom, CML Microcircuits, Conexant, Exstreamer, Integrated Device Technology, Maxim Integrated Исследователи показывают, что слабая связь обеспечивает каркас пресинаптической пластичности, отличительный признак синаптической передачи сигналов в микросхемах гиппокампа.

Забота о микросхемах | Природа неврологии

Микросхемы: интерфейс между нейронами и функцией глобального мозга

- S Grillner &

- A M Graybiel

The MIT Press, 2006 г. 472 стр., Твердая обложка, 55 долларов США.00 ISBN 0262072785 | ISBN: 0-262-07278-5

Поиск в Интернете по запросу «микросхемы» дает более полумиллиона результатов, и эта книга возглавляет список. Откуда такое волнение? Одна из причин заключается в том, что большинство нейробиологов изучают микросхемы в широком смысле слова, что делает этот том интересным. Редакторы дают гибкое рабочее определение (« четко определенные, довольно маленькие образования нервных клеток ») и обрисовывают в общих чертах свою цель — обеспечить мост от генетического и молекулярного уровня к поведенческому и когнитивному уровню не напрямую, а через понимание промежуточных микросхем. .

.

Книга состоит из четырех разделов, в которых рассматриваются микросхемы в двигательной системе, полосатом теле, обонятельной системе и неокортексе. Книга состоит из глав, написанных ведущими экспертами, за которыми следует групповой отчет. В первом разделе рассматриваются колликулярные микросхемы для саккадических движений глаз (Isa и Sparks), а также микросхемы локомоторных позвоночных (Sillar и Grillner) и беспозвоночных (Pfluger и Buschges) и подчеркивается тот факт, что исследователи добились большого прогресса в достижении этой общей цели и что исследователи в совершенно разных системах говорят на одном языке.Групповой отчет (Kiehn) представляет собой элегантную попытку выделить общие принципы проектирования в центральных микросхемах генератора шаблонов в моторных системах, которые адаптированы для многих конкретных задач. Аргумент, эффективно поддерживаемый схемотехникой, состоит в том, что центральные генераторы паттернов включают почти универсальное «ядро», которое состоит из небольшой сети возбуждающих и тормозящих нейронов. Затем базовая микросхема функционально адаптируется к конкретным задачам (например, сегментарно реплицируется и соединяется между собой в опорно-двигательных системах или кардиостимулятор приводится в действие в дыхательных центрах ствола мозга).Нейромодуляция важна для настройки выхода схем.

Затем базовая микросхема функционально адаптируется к конкретным задачам (например, сегментарно реплицируется и соединяется между собой в опорно-двигательных системах или кардиостимулятор приводится в действие в дыхательных центрах ствола мозга).Нейромодуляция важна для настройки выхода схем.

Эти темы развиваются, и новые вводятся в раздел полосатого тела, который знакомит читателей с основными типами клеток, микросхемами и нейромодуляцией в базальных ганглиях (Surmeier, Tepper and Plenz, Bergman, Kimura, Wickens). В групповом отчете (Bolam) обсуждается каноническая микросхема, взаимосвязанная группа нейронов со средними шипами, ГАМКергические интернейроны с быстрым выбросом и гигантский холинергический интернейрон, коллективно иннервируемый кортикостриатными глутаматергическими проекциями и дофаминергическими проекциями черной субстанции.Эта архитектура предлагается в качестве субстрата для «выбора» между различными корковыми входами с помощью хорошо охарактеризованных ионных механизмов, опосредующих состояния «ВВЕРХ» и «ВНИЗ». Допаминергическая и холинергическая модуляция, действующая на каноническую микросхему в сильно дивергентной и конвергентной системе корковых афферентов, предлагается в качестве основы для пластичности, связанной с вознаграждением.

Допаминергическая и холинергическая модуляция, действующая на каноническую микросхему в сильно дивергентной и конвергентной системе корковых афферентов, предлагается в качестве основы для пластичности, связанной с вознаграждением.